Question: Chu's Book Code Examples: Chu's Book Code Examples: 1 Description Problem 1 Design a 2-bit greater-than circuit using gate-level logical operators only This design has

Chu's Book Code Examples:

Chu's Book Code Examples:

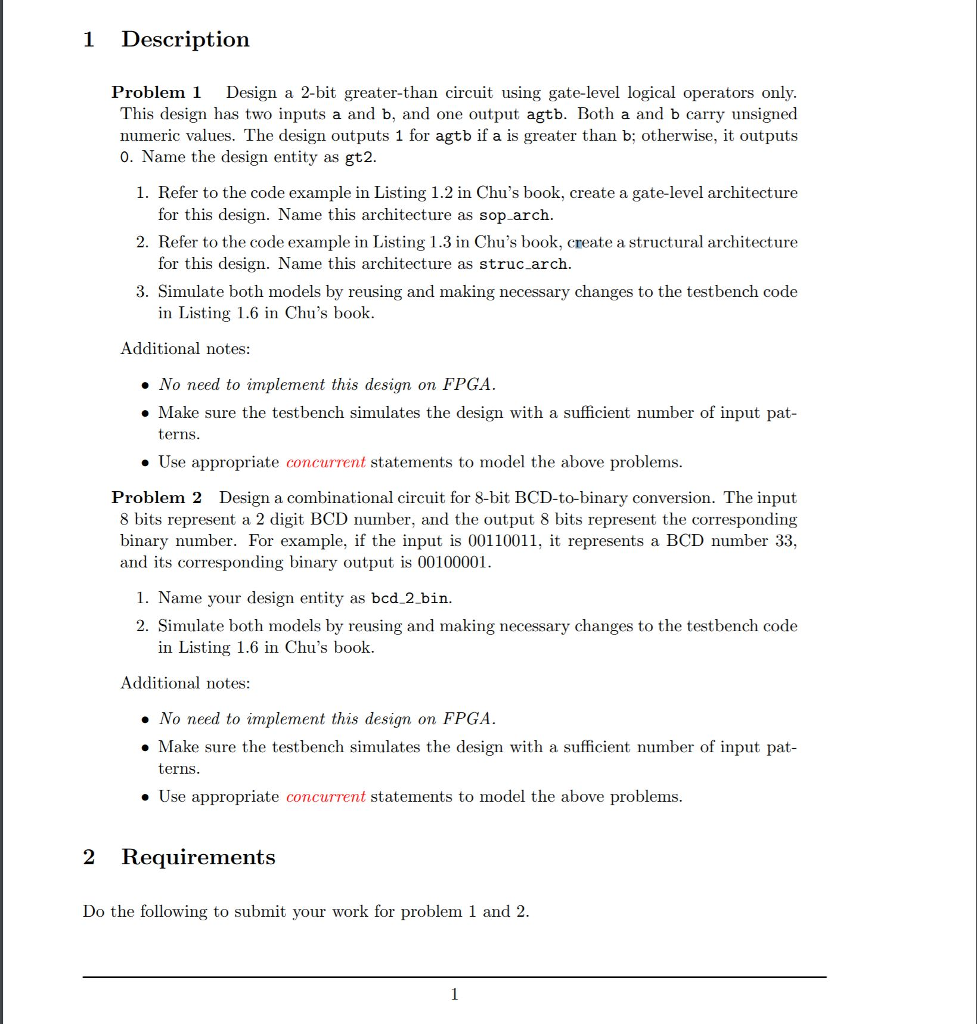

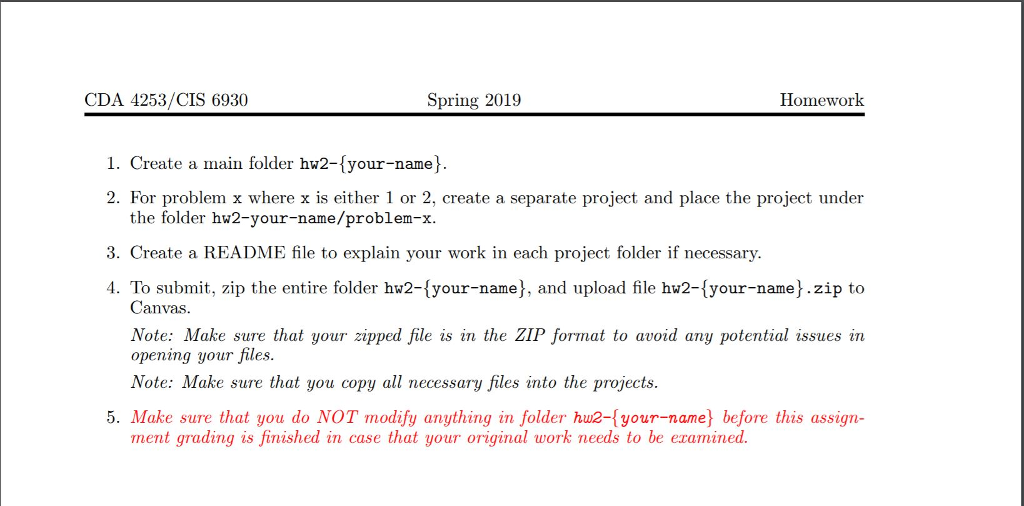

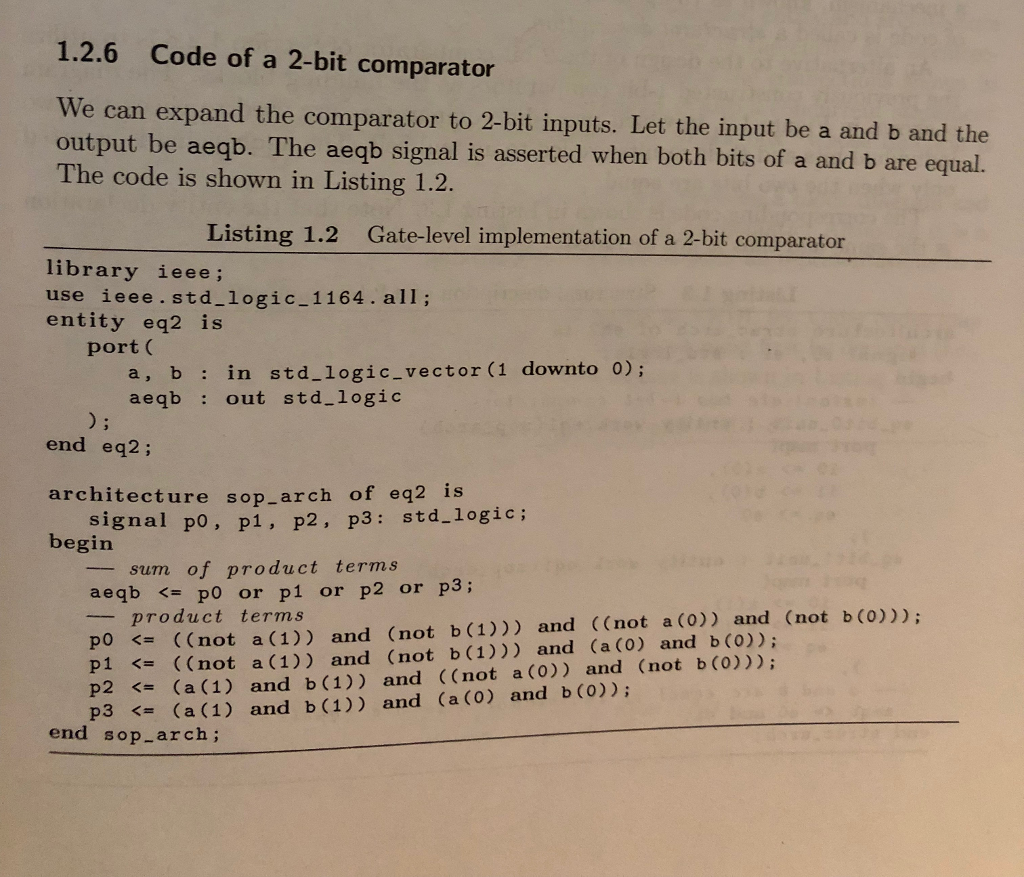

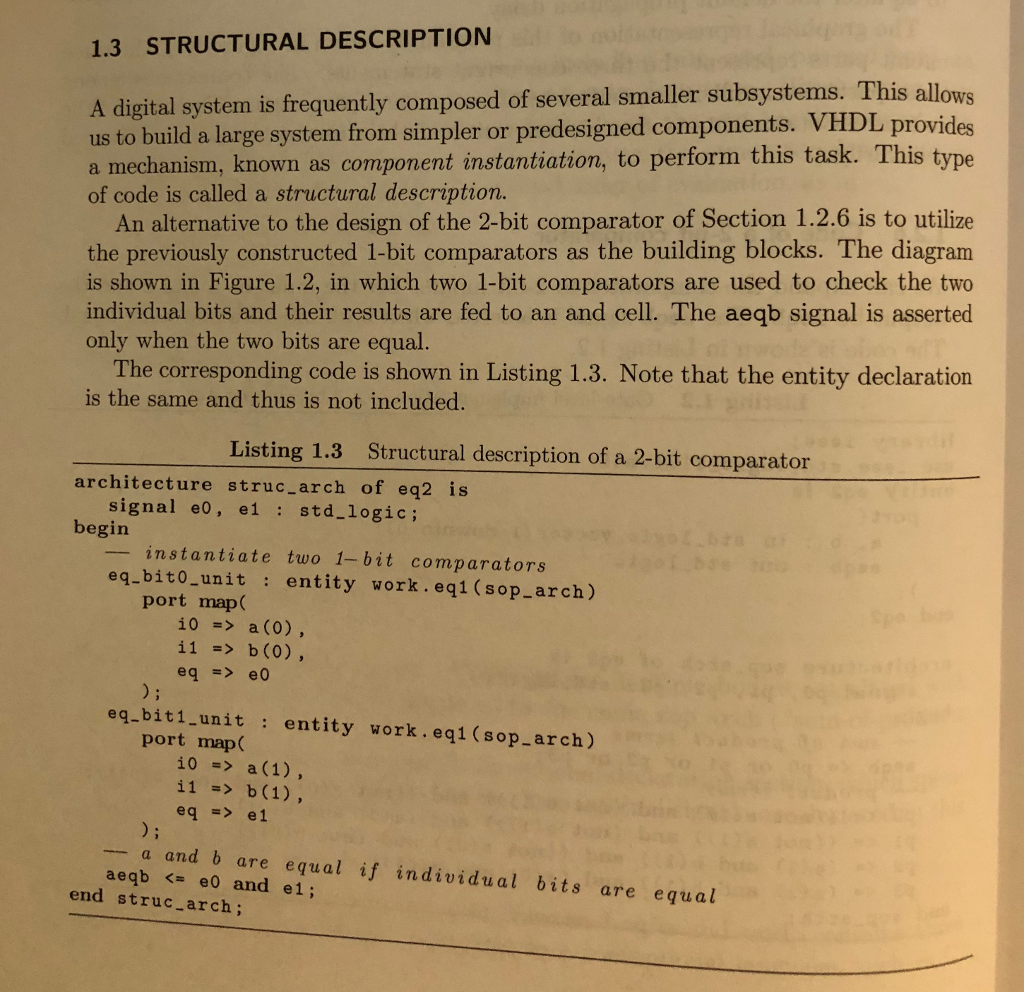

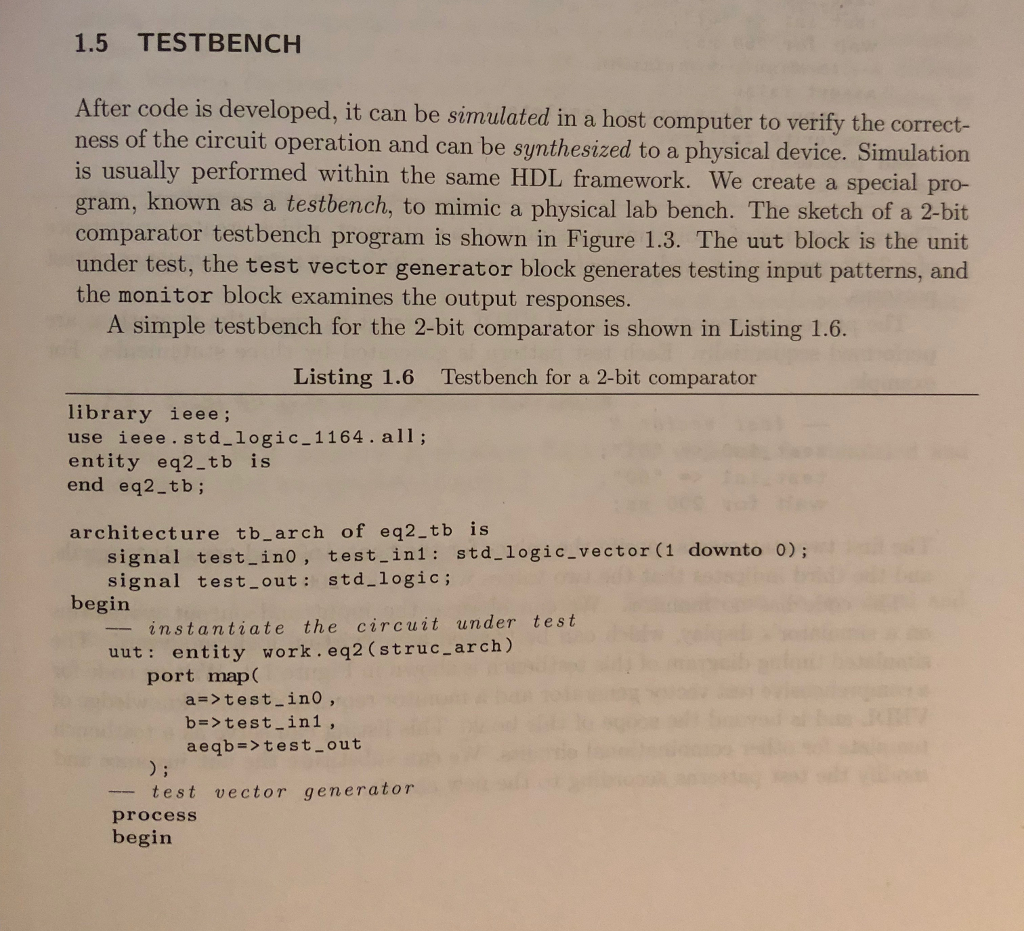

1 Description Problem 1 Design a 2-bit greater-than circuit using gate-level logical operators only This design has two inputs a and b, and one output agtb. Both a and b carry unsigned numeric values. The design outputs 1 for agtb if a is greater than b; otherwise, it outputs 0. Name the design entity as gt2 1. Refer to the code example in Listing 1.2 in Chu's book, create a gate-level architecture 2. Refer to the code example in Listing 1.3 in Chu's book, create a structural architecture 3. Simulate both models by reusing and making necessary changes to the testbench code for this design. Name this architecture as sop arch. for this design. Name this architecture as struc arch. in Listing 1.6 in Chu's book Additional notes No need to implement this design on FPGA Make sure the testbench simulates the design with a sufficient number of input pat- terns Use appropriate concurrent statements to model the above problems. Problem 2 Design a combinational circuit for 8-bit BCD-to-binary conversion. The input 8 bits represent a 2 digit BCD number, and the output 8 bits represent the corresponding binary number. For example, if the input is 00110011, it represents a BCD number 33 and its corresponding binary output is 00100001 1. Name your design entity as bcd 2 bin. 2. Simulate both models by reusing and making necessary changes to the testbench code in Listing 1.6 in Chu's book. Additional notes: . No need to implement this design on FPGA . Make sure the testbench simulates the design with a sufficient number of input pat- terns Use appropriate concurrent statements to model the above problems 2 Requirements Do the following to submit your work for problem 1 and 2 CDA 4253/CIS 6930 Spring 2019 Homework 1. Create a main folder hw2-{your-name). 2. For problem x where x is either 1 or 2, create a separate project and place the project under 3. Create a README file to explain your work in each project folder if necessary. 4. To submit, zip the entire folder hw2-[your-name], and upload file hw2-1your-name.zip to the folder hw2-your-name/problem-x. Canvas. Note: Make sure that your zipped file is in the ZIP fornat to avoid any potential issues in opening your files. Note: Make sure that you copy all necessary files into the projects 5. Make sure that you do NOT modify anything in folder hu2-[your-name] before this assign- ment grading is finished in case that your original work needs to be ezamined. 1.2.6 Code of a 2-bit comparator We can expand the comparator to 2-bit inputs. Let the input be a and b and the output be aeqb. The aeqb signal is asserted when both bits of a and b are equal. The code is shown in Listing 1.2. Listing 1.2 Gate-level implementation of a 2-bit comparator library ieee; use ieee. std.logic.1164. all; entity eq2 is port( a, b in std_logic_vector (1 downto o); aeqb: out std_logic end eq2; architecture sop_arch of eq2 is signal po, p1, p2, p3: std_logic; begin sum of product terms aeqb a (0), i1b(0), eq e0 eq.bit1.unit: entity work.eq1 (sop_arch) port map( i0a(1) _ a and b are equal if individual bits are equal aeqb test ino, b >test in1, aeqb >test_out test vector generator process begin

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts