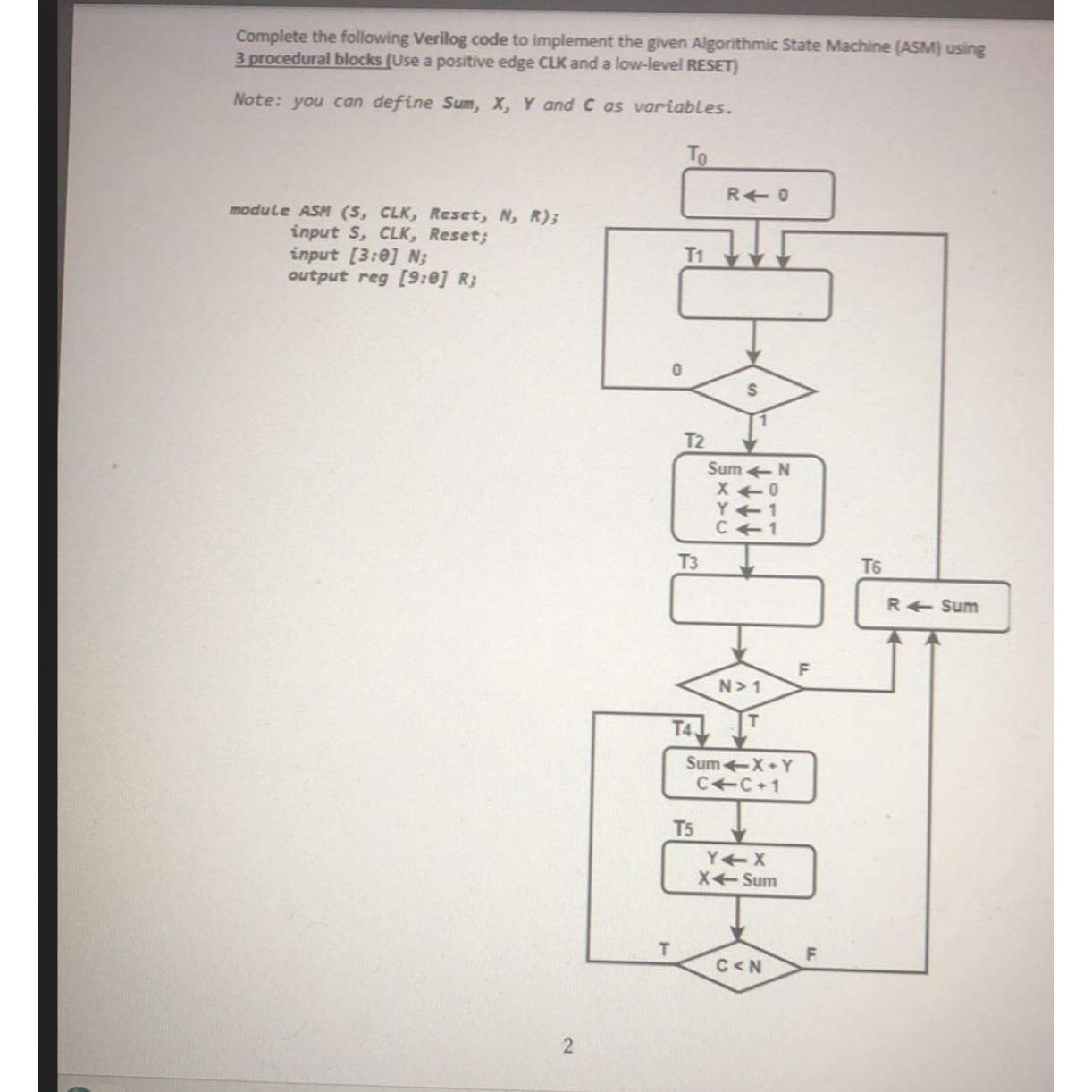

Question: Complete the following Verilog code to implement the given Algorithmic State Machine (ASM) using 3 procedural blocks (Use a positive edge CLK and a

Complete the following Verilog code to implement the given Algorithmic State Machine (ASM) using 3 procedural blocks (Use a positive edge CLK and a low-level RESET) Note: you can define Sum, X, Y and C as variables. module ASM (S, CLK, Reset, N, R); input S, CLK, Reset; input [3:0] N; output reg [9:0] R; 2 T To R40 T1 T2 Sum N X40 Y+1 C+1 T3 T6 R < < Sum F N> 1 T T4 Sum-X+Y C+C+1 T5 Y

Step by Step Solution

3.40 Rating (156 Votes )

There are 3 Steps involved in it

Heres the Verilog code completing the given Algor... View full answer

Get step-by-step solutions from verified subject matter experts