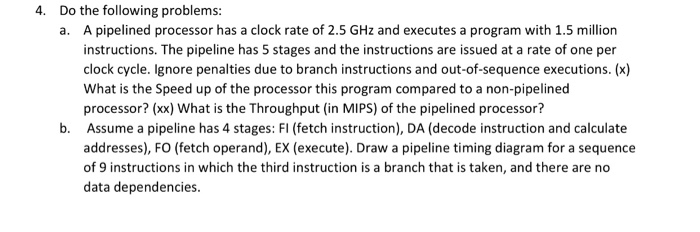

Question: Computer architecture 4. Do the following problems: A pipelined processor has a clock rate of 2.5 GHz and executes a program with 1.5 million instructions.

Computer architecture

Computer architecture 4. Do the following problems: A pipelined processor has a clock rate of 2.5 GHz and executes a program with 1.5 million instructions. The pipeline has 5 stages and the instructions are issued at a rate of one per clock cycle. Ignore penalties due to branch instructions and out-of-sequence executions. (x) What is the Speed up of the processor this program compared to a non-pipelined processor? (xx) What is the Throughput (in MIPS) of the pipelined processor? Assume a pipeline has 4 stages: FI (fetch instruction), DA (decode instruction and calculate addresses), FO (fetch operand), EX (execute). Draw a pipeline timing diagram for a sequence of 9 instructions in which the third instruction is a branch that is taken, and there are no data dependencies. a. b

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts