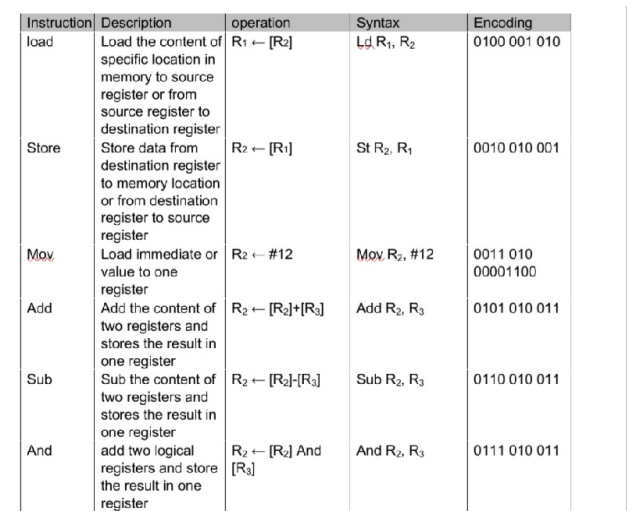

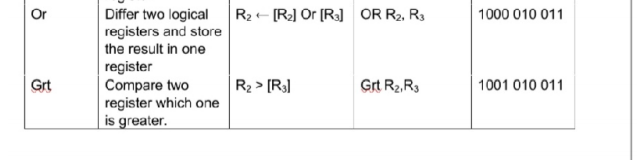

Question: Computer Architecture convert structure set to datapath . . Syntax Ld R1, R2 Encoding 0100 001 010 Store St R2, R1 0010 010 001 Instruction

Computer Architecture

convert structure set to datapath

.

.

![Instruction Description operation load Load the content of R1 (R2] specific location](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f45ee464bfb_10866f45ee406b29.jpg)

Syntax Ld R1, R2 Encoding 0100 001 010 Store St R2, R1 0010 010 001 Instruction Description operation load Load the content of R1 (R2] specific location in memory to source register or from source register to destination register Store data from R2 [R1] destination register to memory location or from destination register to source register Mov Load immediate or R2- #12 value to one register Add Add the content of R2 -- [R2]+[R] two registers and stores the result in one register Sub Sub the content of R2 [R-[R3] two registers and stores the result in one register And add two logical R2 + [R] And registers and store [R] the result in one register Mov Rz, #12 0011 010 00001100 Add R2, R3 0101 010 011 Sub R2, R3 0110 010 011 And R. R 0111 010 011 Or Rz-R] or [R] OR R2, R3 1000 010 011 Differ two logical registers and store the result in one register Compare two register which one is greater Grt R2 > (R) Grt R2,R 1001 010 011 BR Loop 1100 010 001 Branch_if_R2 >R1 The instruction loads a new address into the PC register, and the CPU fetches and executes the new address if the condition is satisfied whereas the next instruction is fetched and the PC is incremental. Clear the content of specific register CL Clear R2 CL R2 1011 010 Syntax Ld R1, R2 Encoding 0100 001 010 Store St R2, R1 0010 010 001 Instruction Description operation load Load the content of R1 (R2] specific location in memory to source register or from source register to destination register Store data from R2 [R1] destination register to memory location or from destination register to source register Mov Load immediate or R2- #12 value to one register Add Add the content of R2 -- [R2]+[R] two registers and stores the result in one register Sub Sub the content of R2 [R-[R3] two registers and stores the result in one register And add two logical R2 + [R] And registers and store [R] the result in one register Mov Rz, #12 0011 010 00001100 Add R2, R3 0101 010 011 Sub R2, R3 0110 010 011 And R. R 0111 010 011 Or Rz-R] or [R] OR R2, R3 1000 010 011 Differ two logical registers and store the result in one register Compare two register which one is greater Grt R2 > (R) Grt R2,R 1001 010 011 BR Loop 1100 010 001 Branch_if_R2 >R1 The instruction loads a new address into the PC register, and the CPU fetches and executes the new address if the condition is satisfied whereas the next instruction is fetched and the PC is incremental. Clear the content of specific register CL Clear R2 CL R2 1011 010

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts