Question: Computer architecture question about asynchronous bus protocol. What happens if the addressed device does not respond due to a malfunction during a read operation? What

Computer architecture question about asynchronous bus protocol.

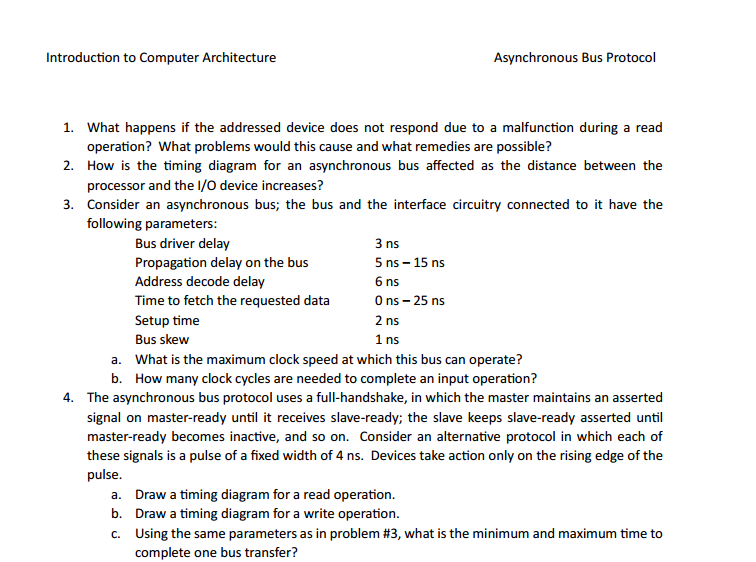

What happens if the addressed device does not respond due to a malfunction during a read operation? What problems would this cause and what remedies are possible? 2. How is the timing diagram for an asynchronous bus affected as the distance between the processor and the I/O device increases? 3. Consider an asynchronous bus; the bus and the interface circuitry connected to it have the following parameters: Bus driver delay 3 ns Propagation delay on the bus 5 ns - 15 ns Address decode delay 6 ns Time to fetch the requested data 0 ns - 25 ns, Setup time 2 ns Bus skew 1 ns a. What is the maximum clock speed at which this bus can operate? b. How many clock cycles are needed to complete an input operation? 4. The asynchronous bus protocol uses a full-handshake, in which the master maintains an asserted signal on master-ready until it receives slave-ready; the slave keeps slave-ready asserted until master-ready becomes inactive, and so on. Consider an alternative protocol in which each of these signals is a pulse of a fixed width of 4 ns. Devices take action only on the rising edge of the pulse. a. Draw a timing diagram for a read operation b. Draw a timing diagram for a write operation. c. Using the same parameters as in problem tt3, what is the minimum and maximum time to complete one bus transfer

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts