Question: Computer Architecture question about multi-cycle bus protocol. Any help would be appriciated! What happens if the addressed device does not respond due to a malfunction

Computer Architecture question about multi-cycle bus protocol. Any help would be appriciated!

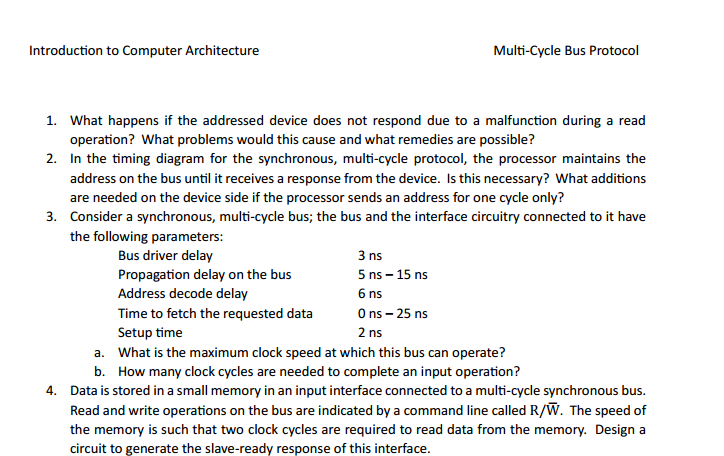

What happens if the addressed device does not respond due to a malfunction during a read operation? What problems would this cause and what remedies are possible? 2. In the timing diagram for the synchronous, multi-cycle protocol, the processor maintains the address on the bus until it receives a response from the device s this necessary? What additions are needed on the device side if the processor sends an address for one cycle only? 3. Consider a synchronous, multi-cycle bus; the bus and the interface circuitry connected to it have the following parameters: Bus driver delay 3 ns Propagation delay on the bus 5 ns -15 ns Address decode delay 6 ns Time to fetch the requested data 0 ns - 25 ns, Setup time 2 ns a. What is the maximum clock speed at which this bus can operate? b. How many clock cycles are needed to complete an input operation? 4. Data is stored in a small memory in an input interface connected to a multi-cycle synchronous bus Read and write operations on the bus are indicated by a command line called R/W. The speed of the memory is such that two clock cycles are required to read data from the memory. Design a circuit to generate the slave-ready response of this interface

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts