Question: Computer system architecture Given a benchmark code that contained 10M lw, 5M sw, 80M arithmetic, 4M branch, 1M jump instructions respectively. Assume memory access takes

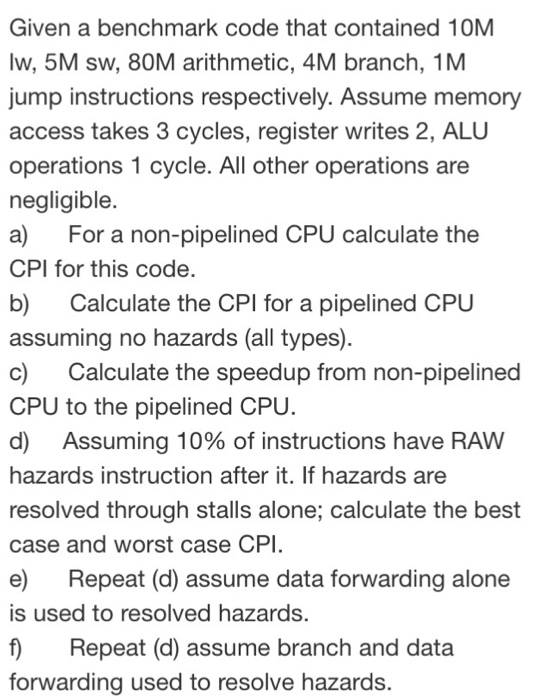

Given a benchmark code that contained 10M lw, 5M sw, 80M arithmetic, 4M branch, 1M jump instructions respectively. Assume memory access takes 3 cycles, register writes 2, ALU operations 1 cycle. All other operations are negligible. a) For a non-pipelined CPU calculate the CPI for this code. b) Calculate the CPl for a pipelined CPU assuming no hazards (all types). c) Calculate the speedup from non-pipelined CPU to the pipelined CPU d) Assuming 10% of instructions have RAW hazards instruction after it. If hazards are resolved through stalls alone; calculate the best case and worst case CPI e) Repeat (d) assume data forwarding alone is used to resolved hazards. f) Repeat (d) assume branch and data forwarding used to resolve hazards

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts