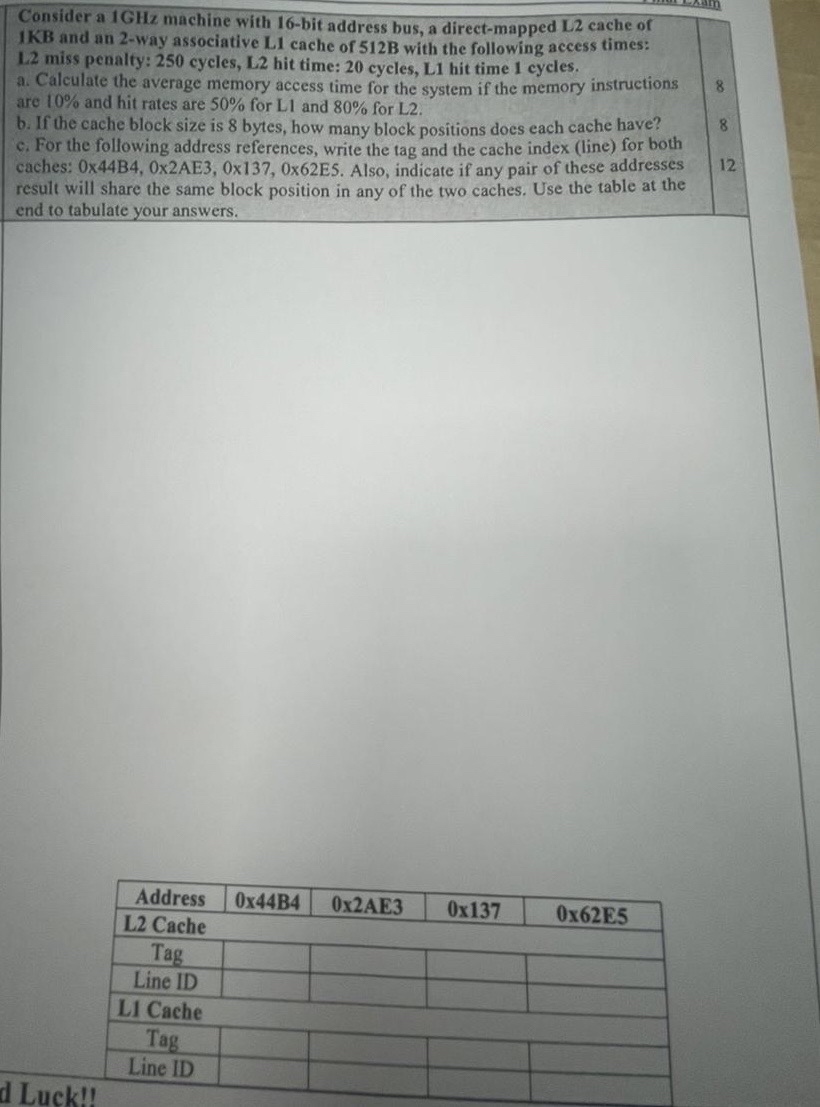

Question: Consider a 1 G H z machine with 1 6 - bit address bus, a direct - mapped L 2 cache of 1 K B

Consider a machine with bit address bus, a directmapped L cache of and an way associative cache of with the following access times: miss penalty: cycles, hit time: cycles, hit time cycles.

a Calculate the average memory access time for the system if the memory instructions are and hit rates are for and for

b If the cache block size is bytes, how many block positions does each cache have? c For the following address references, write the tag and the cache index line for both caches: AE Also, indicate if any pair of these addresses result will share the same block position in any of the two caches. Use the table at the end to tabulate your answers.

tableAddressxBxAExxEL Cache,,TagLine IDL Cache,,,,TagLine ID

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock