Question: Consider a byte-addressed processor architecture with 16KB pages and 36b it physical address. Assume that the synonym problem is solved by using the page offset

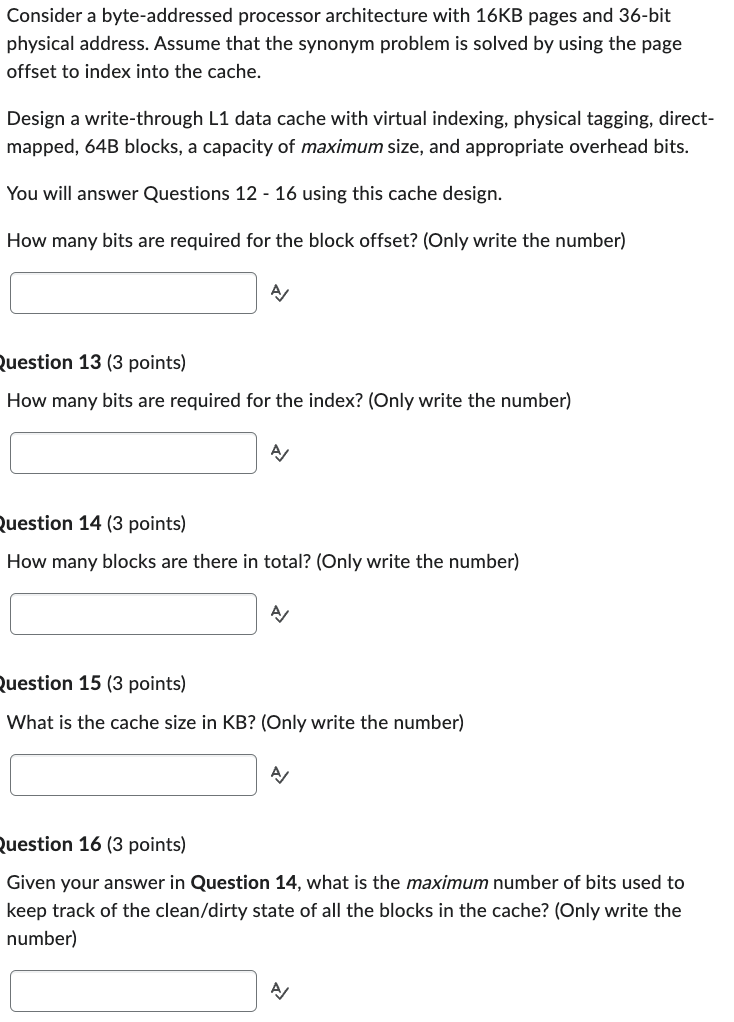

Consider a byte-addressed processor architecture with 16KB pages and 36b it physical address. Assume that the synonym problem is solved by using the page offset to index into the cache. Design a write-through L1 data cache with virtual indexing, physical tagging, directmapped, 64B blocks, a capacity of maximum size, and appropriate overhead bits. You will answer Questions 12 - 16 using this cache design. How many bits are required for the block offset? (Only write the number) A Question 13 (3 points) How many bits are required for the index? (Only write the number) A Question 14 (3 points) How many blocks are there in total? (Only write the number) A Question 15 (3 points) What is the cache size in KB ? (Only write the number) A. Question 16 (3 points) Given your answer in Question 14, what is the maximum number of bits used to keep track of the clean/dirty state of all the blocks in the cache? (Only write the number)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts