Question: Consider a memory system that is composed of one cache and a main memory. The access to the main memory takes 16 ns. Given a

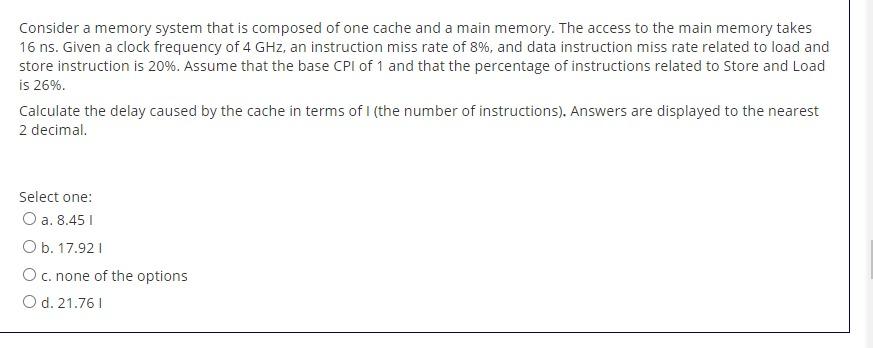

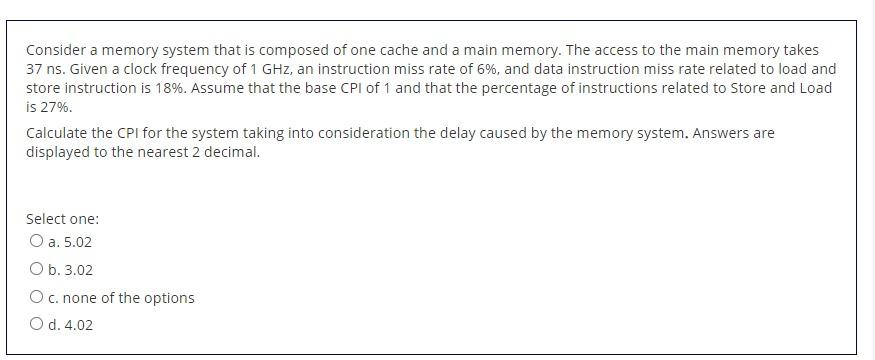

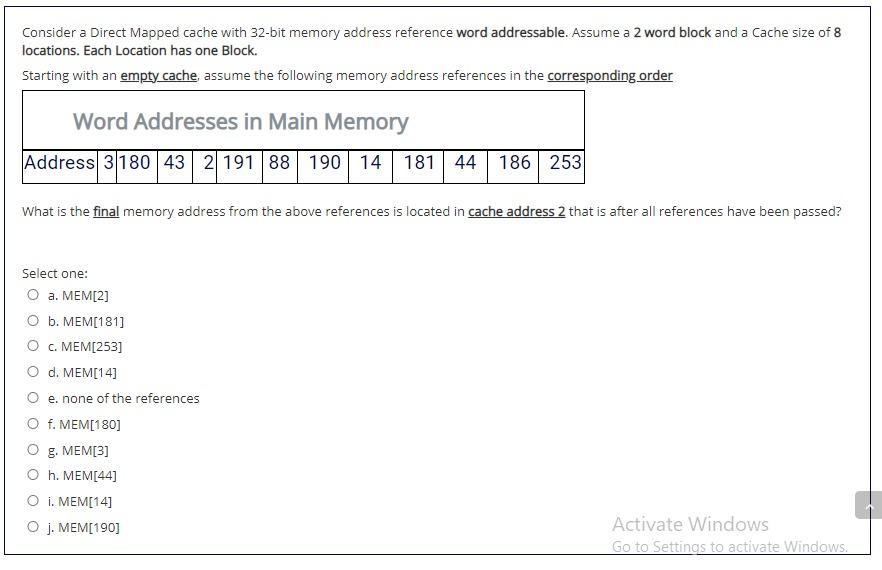

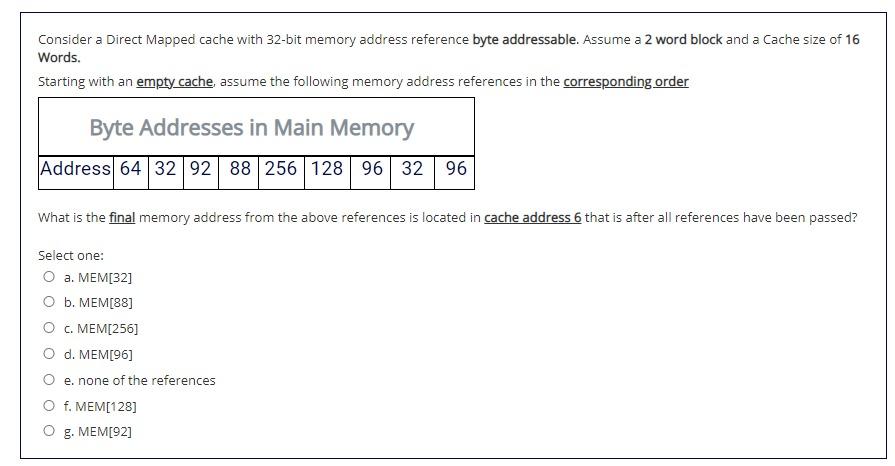

Consider a memory system that is composed of one cache and a main memory. The access to the main memory takes 16 ns. Given a clock frequency of 4 GHz, an instruction miss rate of 8%, and data instruction miss rate related to load and store instruction is 20%. Assume that the base CPI of 1 and that the percentage of instructions related to store and Load is 26%. Calculate the delay caused by the cache in terms of the number of instructions). Answers are displayed to the nearest 2 decimal. Select one: O a. 8.451 O b. 17.921 O c. none of the options O d. 21.761 Consider a memory system that is composed of one cache and a main memory. The access to the main memory takes 37 ns. Given a clock frequency of 1 GHz, an instruction miss rate of 6%, and data instruction miss rate related to load and store instruction is 18%. Assume that the base CPI of 1 and that the percentage of instructions related to store and Load is 27%. Calculate the CPI for the system taking into consideration the delay caused by the memory system. Answers are displayed to the nearest 2 decimal. Select one: O a. 5.02 O b.3.02 O c. none of the options O d. 4.02 Consider a Direct Mapped cache with 32-bit memory address reference word addressable. Assume a 2 word block and a Cache size of 8 locations. Each Location has one Block. Starting with an empty cache, assume the following memory address references in the corresponding order Word Addresses in Main Memory Address 3180 43 2 191 88 190 14181 44 186 253 What is the final memory address from the above references is located in cache address 2 that is after all references have been passed? Select one: O a. MEM[2] b. MEM[181] C. MEM[253] O d. MEM[14] e. none of the references f. MEM[180] g. MEM[3] h. MEM[44] O I. MEM[14] j. MEM[190] Activate Windows Go to Settings to activate Windows Consider a Direct Mapped cache with 32-bit memory address reference byte addressable. Assume a 2 word block and a Cache size of 16 Words. Starting with an empty cache assume the following memory address references in the corresponding order Byte Addresses in Main Memory Address 64 32 92 88 256 128 96 32 96 What is the final memory address from the above references is located in cache address 6 that is after all references have been passed? Select one: O a. MEM[32] O b. MEM[88] OC. MEM[256] O d. MEM[96] e. none of the references O f. MEM[128] g. MEM[92]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts