Question: Consider a pipelined processor that performs the five basic operations of Instruction Fetch, Decode / Register Read, Execute, Memory and Register Write in more than

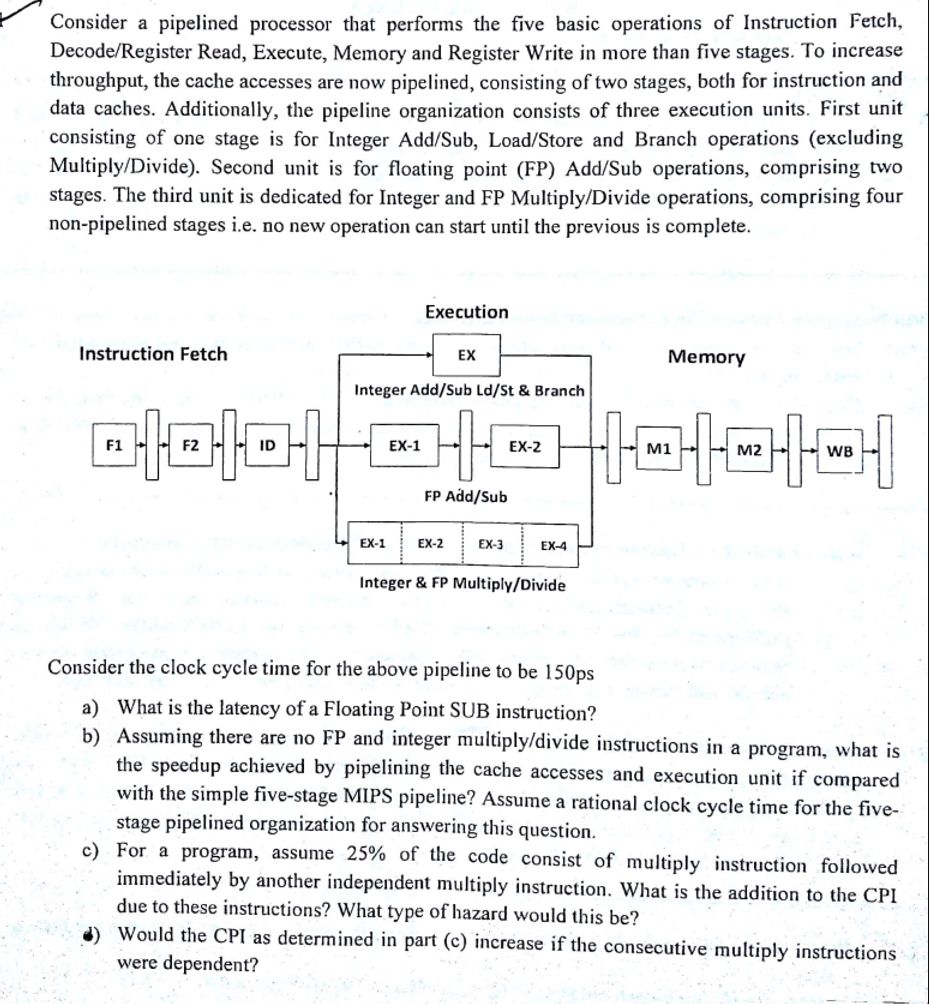

Consider a pipelined processor that performs the five basic operations of Instruction Fetch,

DecodeRegister Read, Execute, Memory and Register Write in more than five stages. To increase

throughput, the cache accesses are now pipelined, consisting of two stages, both for instruction and

data caches. Additionally, the pipeline organization consists of three execution units. First unit

consisting of one stage is for Integer AddSub LoadStore and Branch operations excluding

MultiplyDivide Second unit is for floating point FP AddSub operations, comprising two

stages. The third unit is dedicated for Integer and FP MultiplyDivide operations, comprising four

nonpipelined stages ie no new operation can start until the previous is complete.

Consider the clock cycle time for the above pipeline to be

a What is the latency of a Floating Point SUB instruction?

b Assuming there are no FP and integer multiplydivide instructions in a program, what is

the speedup achieved by pipelining the cache accesses and execution unit if compared

with the simple fivestage MIPS pipeline? Assume a rational clock cycle time for the five

stage pipelined organization for answering this question.

c For a program, assume of the code consist of multiply instruction followed

immediately by another independent multiply instruction. What is the addition to the CPI

due to these instructions? What type of hazard would this be

d Would the CPI as determined in part c increase if the consecutive multiply instructions

were dependent?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock