Question: Consider a system with two-level paging, a 32-bit virtual address space, and a 32-bit physical address space. The page size is 4KB and the system

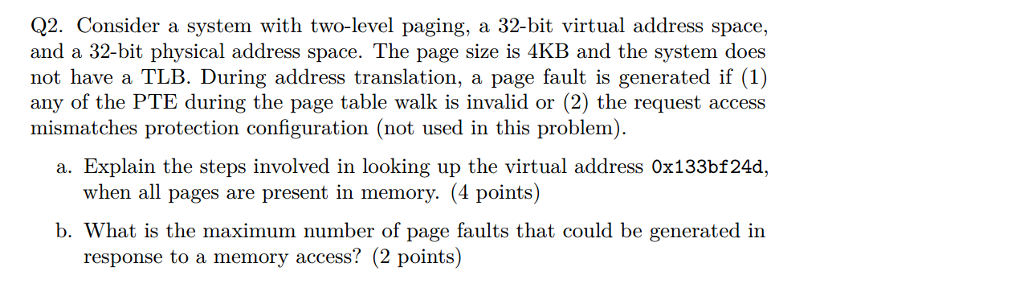

Consider a system with two-level paging, a 32-bit virtual address space, and a 32-bit physical address space. The page size is 4KB and the system does not have a TLB. During address translation, a page fault is generated if (1) any of the PTE during the page table walk is invalid or (2) the request access mismatches protection configuration (not used in this problem). a. Explain the steps involved in looking up the virtual address 0xl33bf24d, when all pages are present in memory. b. What is the maximum number of page faults that could be generated in response to a memory access

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts