Question: Consider changing instruction encoding of the processor given in Table 5-6 in the textbook from mixed of fixed vertical and horizontal formats to just fixed

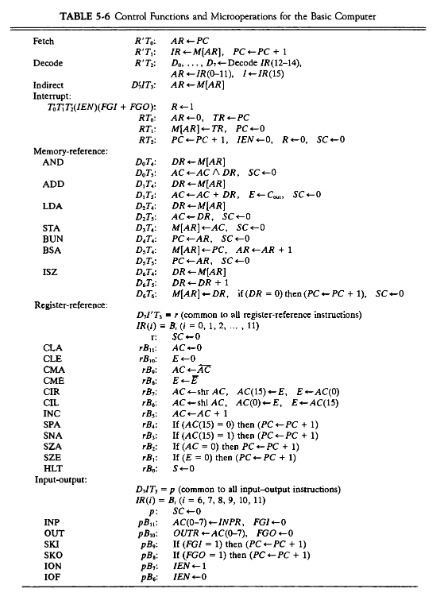

Consider changing instruction encoding of the processor given in Table 5-6 in the textbook from mixed of fixed vertical and horizontal formats to just fixed vertical format. Keep instruction format length 16 bits long by adjusting number of bits allocated to the address field. a) Give instruction format by identifying its fields, number of bits allocated to each field, list of instructions and their corresponding new op codes, list of addressing modes and their corresponding binary codes. b) Rewrite Fetch Cycle, and execute Cycle for instructions ADD, CLA, and INP by listing their micro-operations along with their corresponding control functions. TABLE 5-6 Control Functions and Microoperations for the Basic Computer ADD Feich R'T AR-PC RT: IR --MAR). PC --PC + 1 Decode R'Ts D. ....D.-Decode IR (12-14). AR-IR(0-11). I--IR(15) Indirect DUIT: ARMAR] Interrupt: TETITIEN)(FGI + FGO): R-1 RT: AR-0, IR-P RT: MAR]--TR, PC -- RTS PC - PC + 1, IEN -0. R--0, SC-0 Memory-reference: AND DT.: DR MAR) DT: AC-AC A DR. SC--0 DT. DR-MAR) DT: AC-AC + DR, E SCO LDA DT: DR --MAR) DT: AC-DR, SCO STA DT: MAR --ACSC-0 BUN DTA PC+AR, SC-0 BSA D.T.: MAR-PC. AR-AR + 1 D,T: PC+AR, SCO ISZ D.T.: DR -- M[AR] DT: DR DR + 1 DTs MAR] --DR, (DR = 0) then (PC - PC + 1). SC-0 Register-reference DI'T, -r (common to all register-reference instructions) IR() = B. (i = 0, 1, 2,...,11) T: SC-0 CLA B. AC -- CLE BE0 BACAC B.EE B A C - AC, AC(15) --E, E-AC(0) R AC-shl AC, AC(O)-E, E-AC(15) INC B AC. AC + 1 B. If (AC(15) - ) then (PC +PC+1) By: If (AC(15)-1) then (PC PC + 1) SZA B, IF (AC = 0) then PC - PC + 1) SZE B: (E = 0) then (PC - PC + 1) HLT FRS = Input-output: DJT, (common to all input-output instructions) IR(I) = B. (i = 6, 7, 8, 9, 10, 11) P: SCO pB, AC(0-7) --INPR, FGI-O OUT pBas: OUTR --AC(0-7). FGO--0 pB IF (FG! - 1) then (PC --PC +1) SKO pB. IF (FGO - 1) then (PC --PC +1) PB: JENI 1OF pENO MA CIR CIL SPA SNA INP SKI Consider changing instruction encoding of the processor given in Table 5-6 in the textbook from mixed of fixed vertical and horizontal formats to just fixed vertical format. Keep instruction format length 16 bits long by adjusting number of bits allocated to the address field. a) Give instruction format by identifying its fields, number of bits allocated to each field, list of instructions and their corresponding new op codes, list of addressing modes and their corresponding binary codes. b) Rewrite Fetch Cycle, and execute Cycle for instructions ADD, CLA, and INP by listing their micro-operations along with their corresponding control functions. TABLE 5-6 Control Functions and Microoperations for the Basic Computer ADD Feich R'T AR-PC RT: IR --MAR). PC --PC + 1 Decode R'Ts D. ....D.-Decode IR (12-14). AR-IR(0-11). I--IR(15) Indirect DUIT: ARMAR] Interrupt: TETITIEN)(FGI + FGO): R-1 RT: AR-0, IR-P RT: MAR]--TR, PC -- RTS PC - PC + 1, IEN -0. R--0, SC-0 Memory-reference: AND DT.: DR MAR) DT: AC-AC A DR. SC--0 DT. DR-MAR) DT: AC-AC + DR, E SCO LDA DT: DR --MAR) DT: AC-DR, SCO STA DT: MAR --ACSC-0 BUN DTA PC+AR, SC-0 BSA D.T.: MAR-PC. AR-AR + 1 D,T: PC+AR, SCO ISZ D.T.: DR -- M[AR] DT: DR DR + 1 DTs MAR] --DR, (DR = 0) then (PC - PC + 1). SC-0 Register-reference DI'T, -r (common to all register-reference instructions) IR() = B. (i = 0, 1, 2,...,11) T: SC-0 CLA B. AC -- CLE BE0 BACAC B.EE B A C - AC, AC(15) --E, E-AC(0) R AC-shl AC, AC(O)-E, E-AC(15) INC B AC. AC + 1 B. If (AC(15) - ) then (PC +PC+1) By: If (AC(15)-1) then (PC PC + 1) SZA B, IF (AC = 0) then PC - PC + 1) SZE B: (E = 0) then (PC - PC + 1) HLT FRS = Input-output: DJT, (common to all input-output instructions) IR(I) = B. (i = 6, 7, 8, 9, 10, 11) P: SCO pB, AC(0-7) --INPR, FGI-O OUT pBas: OUTR --AC(0-7). FGO--0 pB IF (FG! - 1) then (PC --PC +1) SKO pB. IF (FGO - 1) then (PC --PC +1) PB: JENI 1OF pENO MA CIR CIL SPA SNA INP SKI

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts