Question: Consider Intrinsity FastMath Processor that implements MIPS 32 instruction set architecture. Its virtual addresses are 32-bit integers. It uses 16 KB pages. The processor

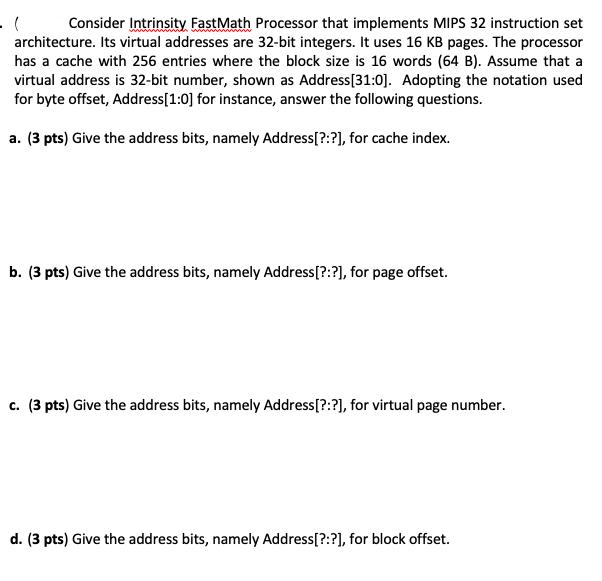

Consider Intrinsity FastMath Processor that implements MIPS 32 instruction set architecture. Its virtual addresses are 32-bit integers. It uses 16 KB pages. The processor has a cache with 256 entries where the block size is 16 words (64 B). Assume that a virtual address is 32-bit number, shown as Address [31:0]. Adopting the notation used for byte offset, Address [1:0] for instance, answer the following questions. a. (3 pts) Give the address bits, namely Address[?:?], for cache index. b. (3 pts) Give the address bits, namely Address[?:?], for page offset. c. (3 pts) Give the address bits, namely Address[?:?], for virtual page number. d. (3 pts) Give the address bits, namely Address[?:?], for block offset.

Step by Step Solution

3.59 Rating (152 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts