Question: Consider the following code segment on the 5-stage Pipelined MIPS architecture we discussed in class: Loop: lw $t0, 0($s1) addu $t0, $t0, $s2 sw $t0,

Consider the following code segment on the 5-stage Pipelined MIPS architecture we discussed in class:

Loop: lw $t0, 0($s1) addu $t0, $t0, $s2 sw $t0, 0($s1) addi $s1, $s1, -4 bne $s1, $zero, Loop

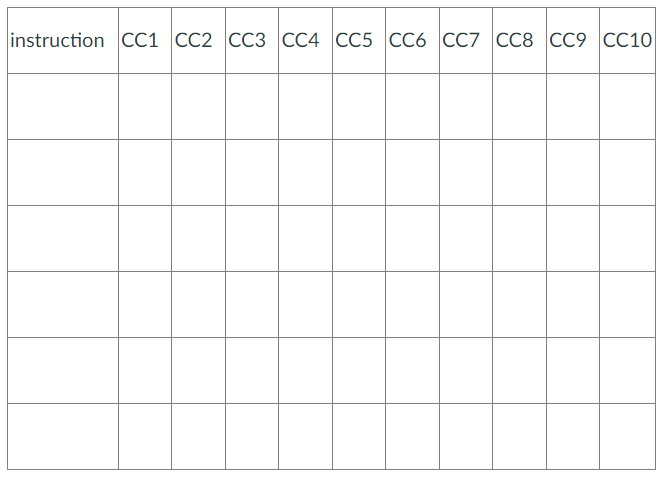

Fill the pipeline schedule below for one iteration of the loop. Mark all hazards (e.g. you may use arrows). Assume forwarding between the pipeline stages is used whenever possible. Mark all data forwards. Also assume that the static "branch not taken" prediction strategy is used and that there is a 1 cycle penalty for branch misspredictions. Assume the loop is executed 10 times.

\begin{tabular}{|l|l|l|l|l|l|l|l|l|l|l|} \hline instruction & CC1 & CC2 & CC3 & CC4 & CC5 & CC6 & CC7 & CC8 & CC9 & CC10 \\ \hline & & & & & & & & & & \\ \hline & & & & & & & & & & \\ \hline & & & & & & & & & & \\ \hline & & & & & & & & & & \\ \hline \end{tabular}

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts