Question: Consider the following code sequence executing on a Single-issue CPU using Tomasulos algorithm with Reorder Buffer. L.D F1, 0(F0) L.D F2, 4(F0) L.D F3, 8(F0)

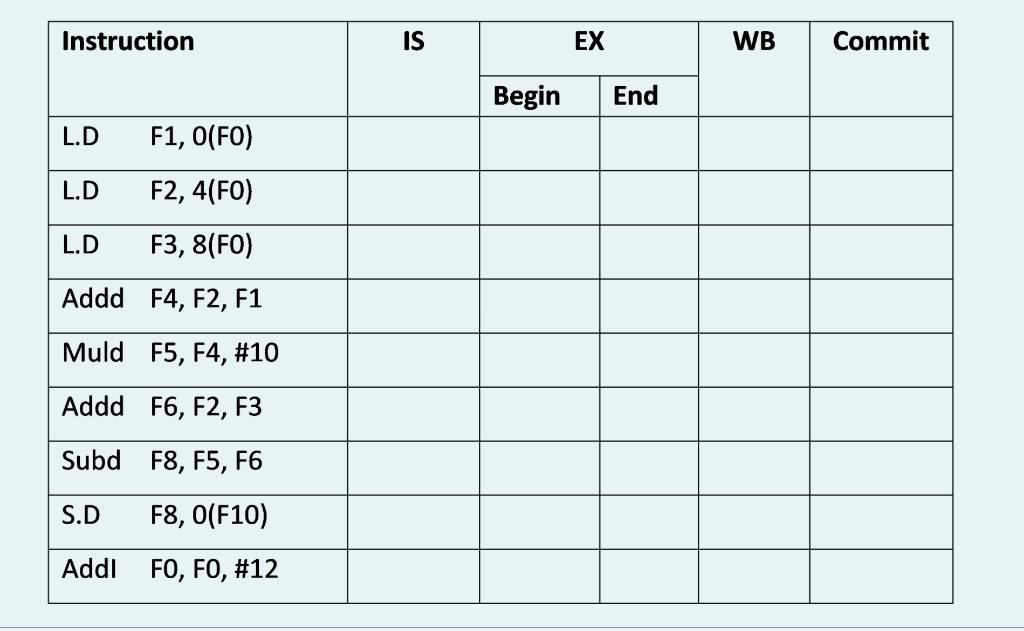

Consider the following code sequence executing on a Single-issue CPU using Tomasulo’s algorithm with Reorder Buffer. L.D F1, 0(F0) L.D F2, 4(F0) L.D F3, 8(F0) Addd F4, F2, F1 Mild F5, F4, #10 Addd F6, F2, F3 Subd F8, F5, F6 S.D F8, 0(F10) AddI F0, F0, #12 Assume the following 1. The architecture has one Floating Point adder/subtractor (for addd and subd instructions), one Floating Point Multiplier (for Muld instruction), two integer addition units (for integer addition operations (AddI) and memory address calculation (L.D and S.D), one unit for load and one unit for the store. 2. All functional units have two reservation stations. 3. Assume the following: execution of the Muld instruction requires 8 clock cycles while Addd and Subd require 3 clock cycles. All integer units require 1 clock cycle. Read/Write on memory takes 2 cycles. 4. Assume that only one CDB is available.

Instruction IS EX WB Commit Begin End L.D F1, 0(F0) L.D F2, 4(F0) L.D F3, 8(F0) Addd F4, F2, F1 Muld F5, F4, #10 Addd F6, F2, F3 Subd F8, F5, F6 S.D F8, 0(F10) Addl FO, FO, #12

Step by Step Solution

3.49 Rating (146 Votes )

There are 3 Steps involved in it

Assume the following 1 The architecture has one Floating Point addersubtractor for addd and subd ins... View full answer

Get step-by-step solutions from verified subject matter experts