Question: Consider the following codes. I) Loop: L.D II) Loop: f0, 0(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) ADDI rl, r1, #23-8 BNE rl,

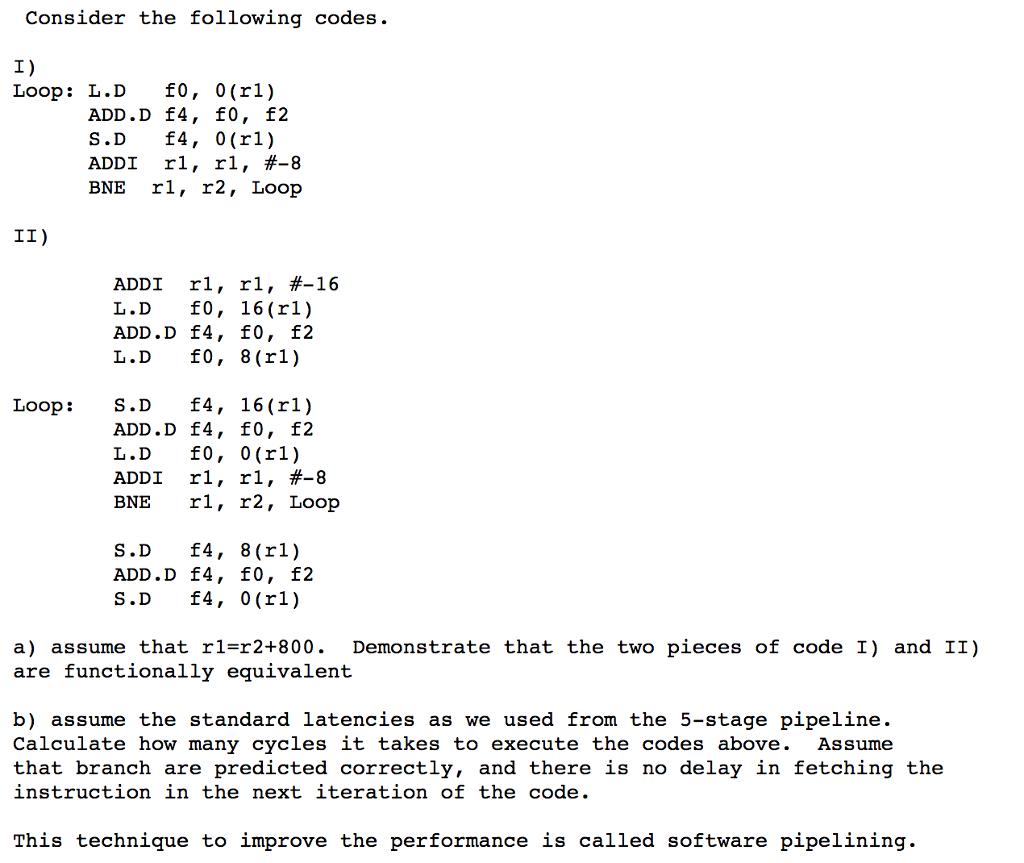

Consider the following codes. I) Loop: L.D II) Loop: f0, 0(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) ADDI rl, r1, #23-8 BNE rl, r2, Loop ADDI rl, r1, #2-16 L.D f0, 16(rl) ADD.D f4, f0, f2 L.D f0, 8(rl) S.D f4, 16(rl) ADD.D f4, f0, f2 L.D f0, 0(rl) ADDI rl, r1, #23-8 BNE r1, r2, Loop S.D f4, 8(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) a) assume that rl=r2+800. Demonstrate that the two pieces of code I) and II) are functionally equivalent b) assume the standard latencies as we used from the 5-stage pipeline. Calculate how many cycles it takes to execute the codes above. Assume that branch are predicted correctly, and there is no delay in fetching the instruction in the next iteration of the code. This technique to improve the performance is called software pipelining.

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts