Question: for computer architecture 1 Question#2: Consider the following code fragment: Loop: LD FO, O(R1) LD F1, O(R2) MULTD F2, F, F1 ADDD F3, F3, F2

for computer architecture

for computer architecture

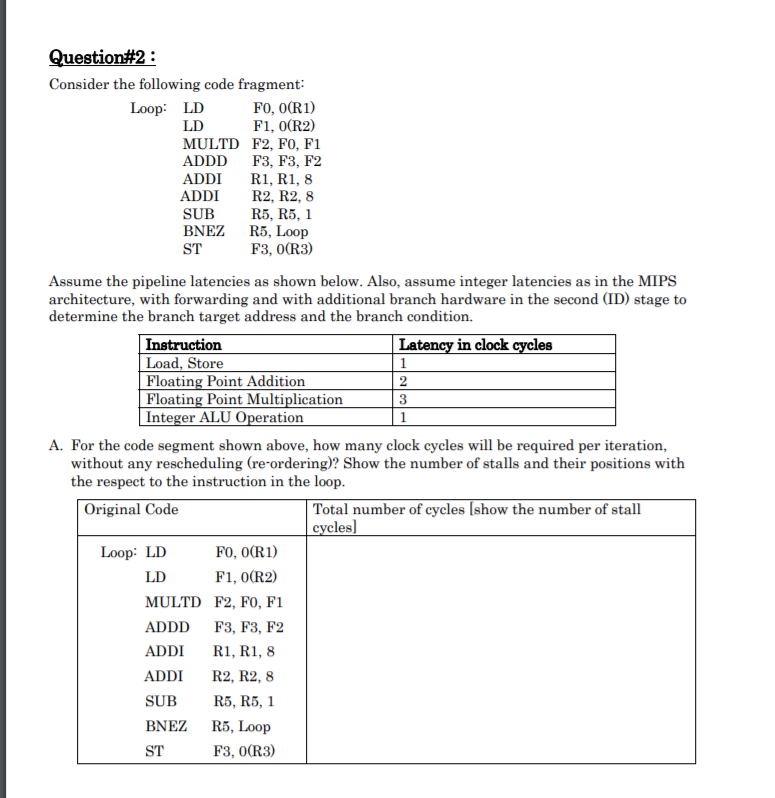

1 Question#2: Consider the following code fragment: Loop: LD FO, O(R1) LD F1, O(R2) MULTD F2, F, F1 ADDD F3, F3, F2 ADDI R1, R1, 8 ADDI R2, R2, 8 SUB R5, R5, 1 BNEZ R5, Loop ST F3, O(R3) Assume the pipeline latencies as shown below. Also, assume integer latencies as in the MIPS architecture, with forwarding and with additional branch hardware in the second (ID) stage to determine the branch target address and the branch condition. Instruction Latency in clock cycles Load, Store Floating Point Addition 2 Floating Point Multiplication 3 Integer ALU Operation 1 A. For the code segment shown above, how many clock cycles will be required per iteration, without any rescheduling (re-ordering)? Show the number of stalls and their positions with the respect to the instruction in the loop. Original Code Total number of cycles (show the number of stall cycles) Loop: LD FO, O(R1) LD F1, O(R2) MULTD F2, FO, F1 ADDD F3, F3, F2 ADDI R1, R1, 8 ADDI R2, R2, 8 SUB R5, R5, 1 BNEZ R5, Loop F3, O(R3) ST 1 Question#2: Consider the following code fragment: Loop: LD FO, O(R1) LD F1, O(R2) MULTD F2, F, F1 ADDD F3, F3, F2 ADDI R1, R1, 8 ADDI R2, R2, 8 SUB R5, R5, 1 BNEZ R5, Loop ST F3, O(R3) Assume the pipeline latencies as shown below. Also, assume integer latencies as in the MIPS architecture, with forwarding and with additional branch hardware in the second (ID) stage to determine the branch target address and the branch condition. Instruction Latency in clock cycles Load, Store Floating Point Addition 2 Floating Point Multiplication 3 Integer ALU Operation 1 A. For the code segment shown above, how many clock cycles will be required per iteration, without any rescheduling (re-ordering)? Show the number of stalls and their positions with the respect to the instruction in the loop. Original Code Total number of cycles (show the number of stall cycles) Loop: LD FO, O(R1) LD F1, O(R2) MULTD F2, FO, F1 ADDD F3, F3, F2 ADDI R1, R1, 8 ADDI R2, R2, 8 SUB R5, R5, 1 BNEZ R5, Loop F3, O(R3) ST

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts