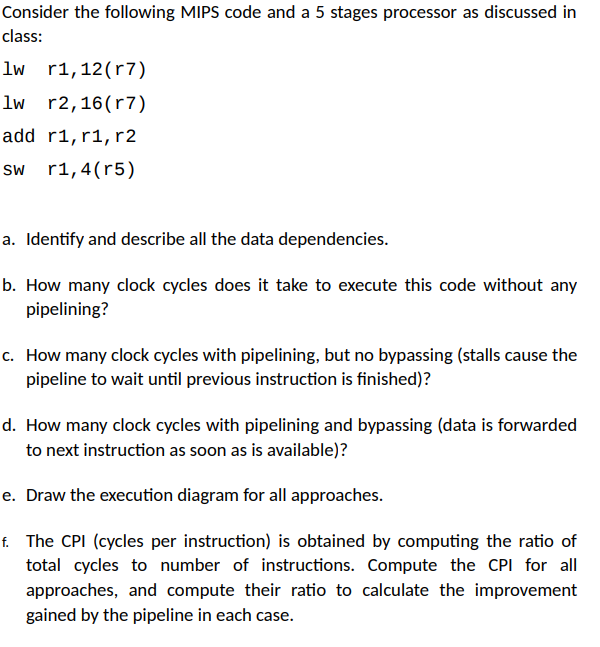

Question: Consider the following MIPS code and a 5 stages processor as discussed in class: lw r1, 12(r7) lw r2,16 (r7) add ri,ri, r2 sw r1,4(r5)

Consider the following MIPS code and a 5 stages processor as discussed in class: lw r1, 12(r7) lw r2,16 (r7) add ri,ri, r2 sw r1,4(r5) a. Identify and describe all the data dependencies. b. How many clock cycles does it take to execute this code without any pipelining? How many clock cycles with pipelining, but no bypassing (stalls cause the pipeline to wait until previous instruction is finished)? c. d. How many clock cycles with pipelining and bypassing (data is forwarded to next instruction as soon as is available)? e. Draw the execution diagram for all approaches. f. The CPI (cycles per instruction) is obtained by computing the ratio of total cycles to number of instructions. Compute the CPl for all approaches, and compute their ratio to calculate the improvement gained by the pipeline in each case

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts