Question: Subject - Computer Organization and Architecture [ Theory ] Before Solving this problem, please go through all the requirements. It's my kind request to you.

Subject - Computer Organization and Architecture [ Theory ]

Before Solving this problem, please go through all the requirements. It's my kind request to you.

I added sample questions and answers for your better understanding. from all of them, here is one red-quark question! You have to solve that question only. Please follow this pattern. Without this method, our instructor does not accept any solution. Please, take enough time, approximately 10-12 hrs for solving, but don't write irrelevant something. Please try to understand my situation.

![Subject - Computer Organization and Architecture [ Theory ] Before Solving this](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f5174c710ac_31566f5174be4957.jpg)

# I have posted this question several times, but one of your experts solved the wrong number with an irrelevant answer. It's too much pathetic for me. Did I purchase it for it? You can take enough time to solve this problem, and if you don't have enough knowledge to solve this answer, please skip it.

Hi Experts! Would you please try to solve this as soon as possible with 100 % Accuracy? If possible, please do it.

You have to follow some instructions which I mentioned below. If you don't follow my instructions, please skip my questions.

You have to answer only #3 RED MARKS. I repeated, don't do other numbers.

Instructions are given,

- You need to show detailed calculations, as required.

- You need to provide clear diagrams, as required. All diagrams should be clearly drawn

Question --------

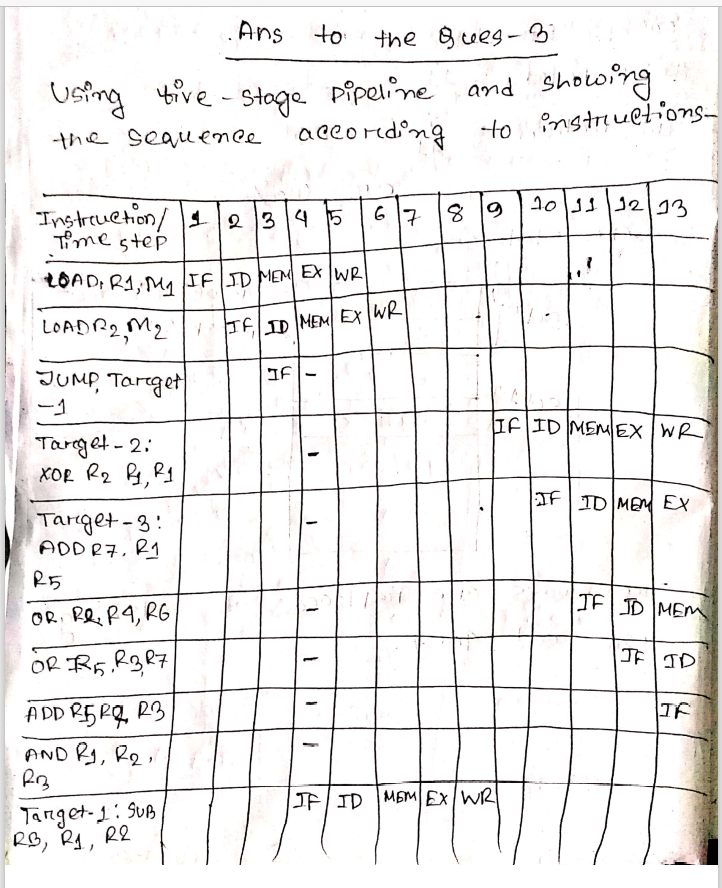

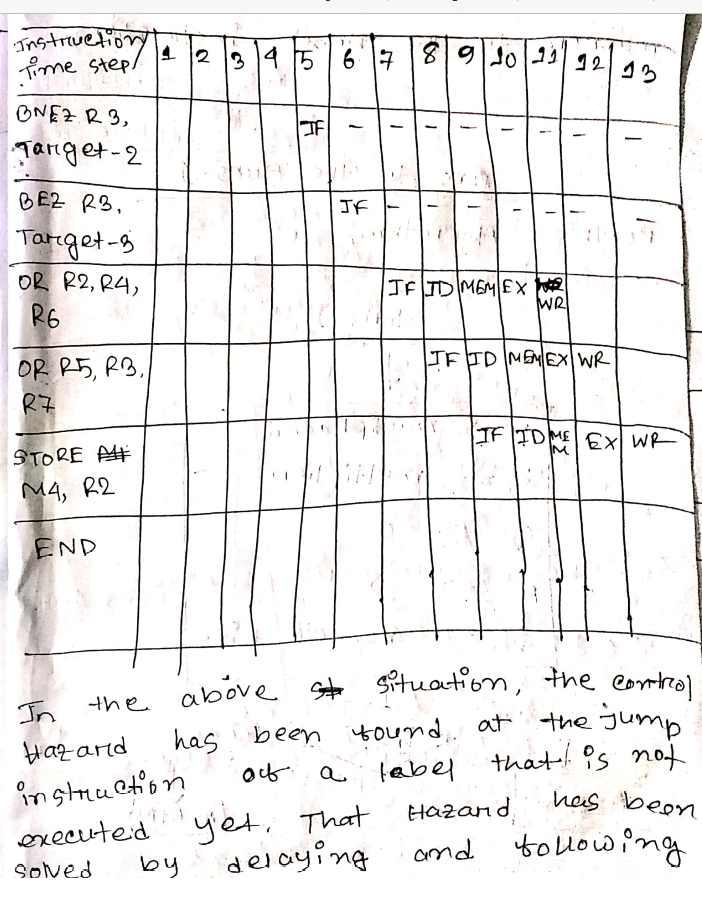

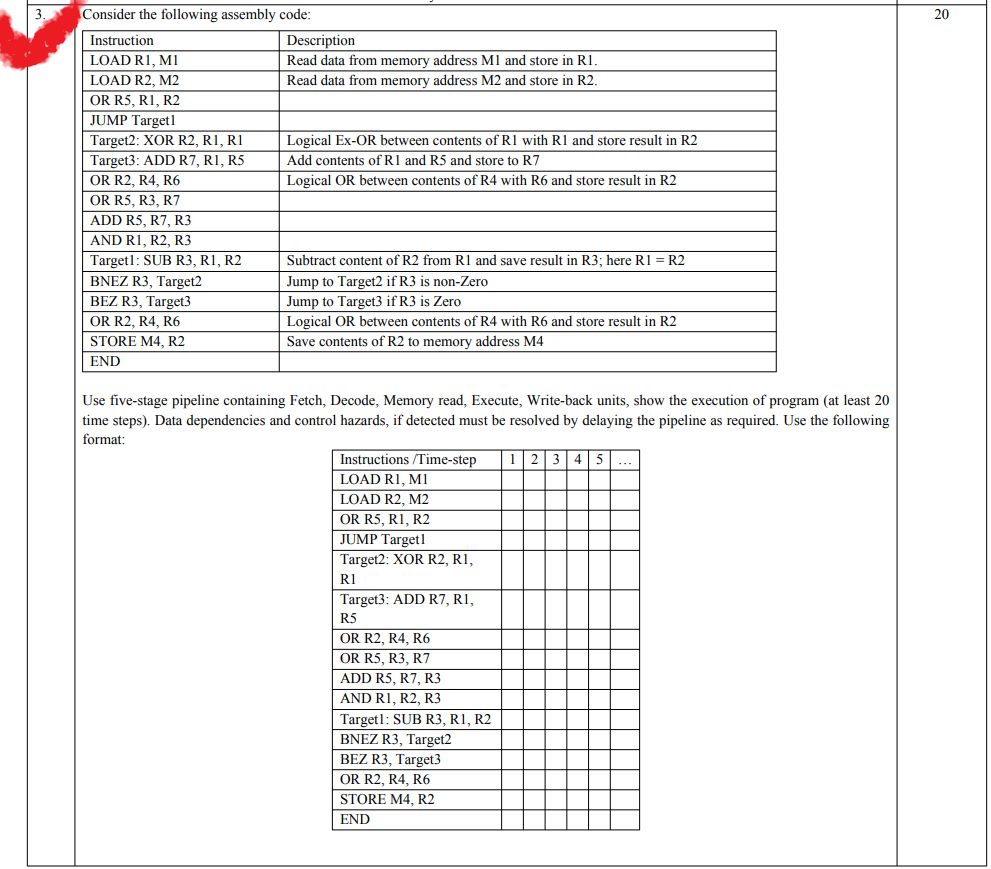

3. 20 Consider the following assembly code: Instruction Description LOAD RI, MI Read data from memory address Ml and store in RI. LOAD R2, M2 Read data from memory address M2 and store in R2. JUMP Target1 Target2: XOR R2, R1, RI Logical Ex-OR between contents of Rl with RI and store result in R2 Target3: ADD R7, RI, R5 Add contents of R1 and R5 and store to R7 OR R2, R4, R6 Logical OR between contents of R4 with R6 and store result in R2 OR R5, R3, R7 ADD RS, R7, R3 AND RI, R2, R3 TargetI: SUB R3, R1, R2 Subtract content of R2 from Rl and save result in R3; here R1 = R2 BNEZ R3, Target2 Jump to Target2 if R3 is non-Zero BEZ R3, Target3 Jump to Target3 if R3 is Zero OR R2, R4, R6 Logical OR between contents of R4 with R6 and store result in R2 OR RS, R3, R7 STORE M4, R2 Save contents of R2 to memory address M4 END Use five-stage pipeline containing Fetch, Decode, Memory read, Execute, Write-back units, show the execution of program (at least 20 time steps). Data dependencies and control hazards, if detected must be resolved by delaying the pipeline as required. Use the following format: Instructions /Time-step 12345 LOAD RI, MI LOAD R2, M2 JUMP Target-1 Target-2: XOR R2, RI, RI Target-3: ADD R7, R1, R5 OR R2, R4, R6 OR R5, R3, R7 ADD R5, R7, R3 AND RI, R2, R3 Target-1: SUB R3, R1, R2 BNEZ R3, Target-2 BEZ R3, Target-3 OR R2, R4, R6 OR R5, R3, R7 STORE M4, R2 END Ans to the gues-3 Using tive - stage pipeline and showing according to instructions, the sequence solus 12/13 Instruction is 1 2 3 4 5 6 17 18 19 time step LOAD, R1, My IFJD MEN EX WR LOADR2 M2 IF ID MEM EX|WR , . IF - JUMP, Torget -1 Target - 2: XOR R2 R4, R1 IF ID MEMEX WR - 21F1D ME EX Target-3 ADDR7, R1 R5 OR. RL, R4, RG OR R5. R3 R7 JFD MEM - - IJF ID - IF ADD RGRO, R3 AND R1, R2, Ro 1 JAID MEM EXWR Tanget-1: SUB RB, R1, R2 To trimester 12 13 14 15 16 17 1819 $0 3392133 ! IF 1 - BNEZ. R3, Target-2 - JF - - BEZ RS, Target-gi OR R2, R4, R6 IF IDMGMEX WR IED MY EX WR OR R5, RB, R7 IF IDME EX WR M STORE A M4, R2 END In the above Hazard has instruction executed yet. That Hazard by delaying sta situation, the control been bound at the jump ! of a a label that is not and has bee of Solved 3. 20 Consider the following assembly code: Instruction Description LOAD RI, MI Read data from memory address Ml and store in RI. LOAD R2, M2 Read data from memory address M2 and store in R2. OR R5, R1, R2 JUMP Target1 Target2: XOR R2, RI, RI Logical Ex-OR between contents of Rl with Rl and store result in R2 Target3: ADD R7, RI, R5 Add contents of Rl and R5 and store to R7 OR R2, R4, R6 Logical OR between contents of R4 with R6 and store result in R2 OR R5, R3, R7 ADD R5, R7, R3 AND RI, R2, R3 Targetl: SUB R3, R1, R2 Subtract content of R2 from Rl and save result in R3; here RI R2 BNEZ R3, Target2 Jump to Target2 if R3 is non-Zero BEZ R3, Target3 Jump to Target3 if R3 is Zero OR R2 R4, R6 Logical OR between contents of R4 with R6 and store result in R2 STORE M4, R2 Save contents of R2 to memory address M4 END Use five-stage pipeline containing Fetch, Decode, Memory read, Execute, Write-back units, show the execution of program (at least 20 time steps). Data dependencies and control hazards, if detected must be resolved by delaying the pipeline as required. Use the following format: Instructions /Time-step 112 45 LOAD RI, MI LOAD R2, M2 OR R5, R1, R2 JUMP Target! Target2: XOR R2, RI, RI Target3: ADD R7, RI, R5 OR R2, R4, R6 OR R5, R3, R7 ADD RS, R7, R3 AND RI, R2, R3 Targetl: SUB R3, R1, R2 BNEZ R3, Target2 BEZ R3, Target3 OR R2, R4, R6 STORE M4, R2 END

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts