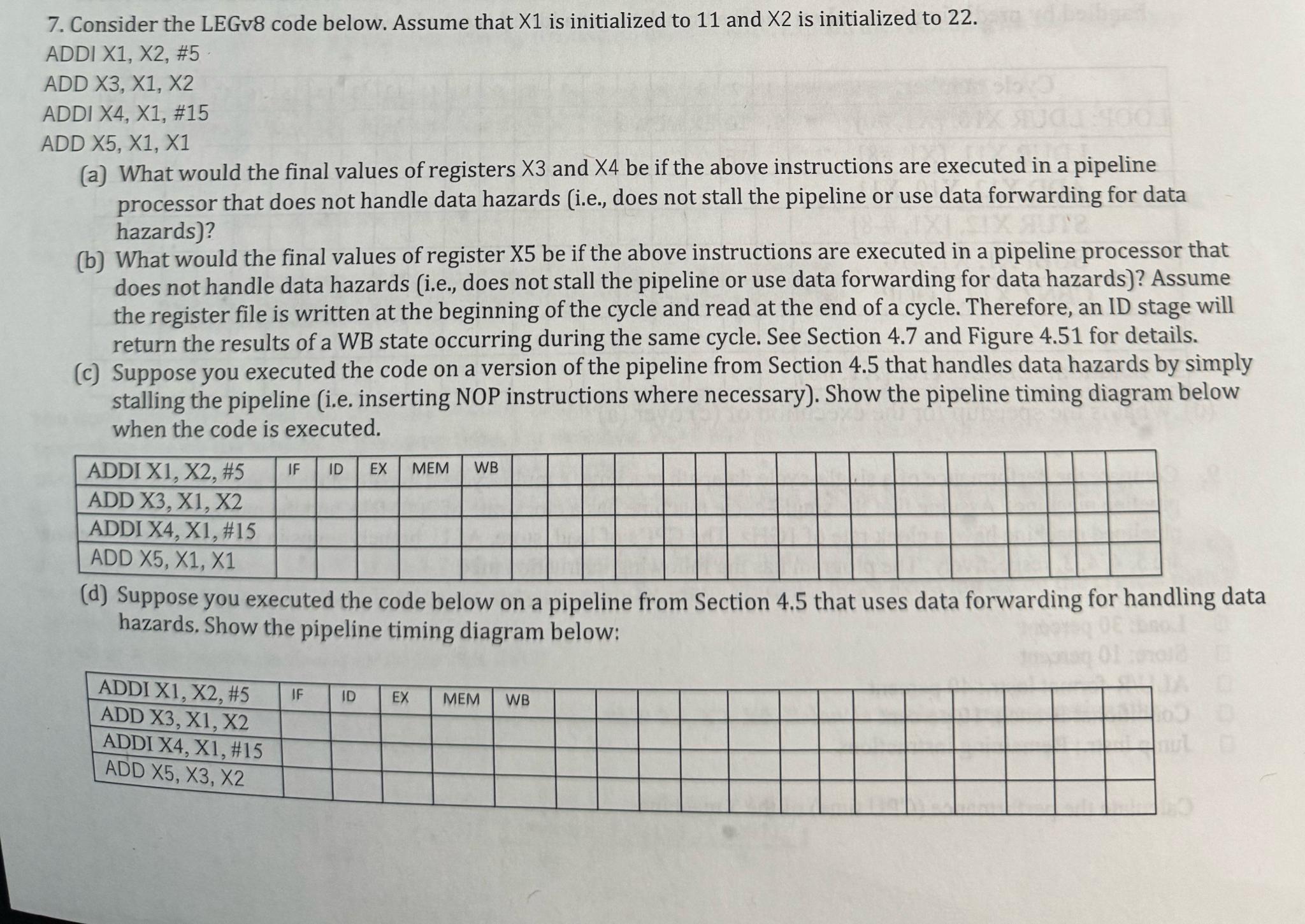

Question: Consider the LEGv 8 code below. Assume that x 1 is initialized to 1 1 and x 2 is initialized to 2 2 . ADDI

Consider the LEGv code below. Assume that is initialized to and is initialized to

ADDI #

ADDx

ADDI #

ADD

a What would the final values of registers and be if the above instructions are executed in a pipeline processor that does not handle data hazards ie does not stall the pipeline or use data forwarding for data hazards

b What would the final values of register be if the above instructions are executed in a pipeline processor that does not handle data hazards ie does not stall the pipeline or use data forwarding for data hazards Assume the register file is written at the beginning of the cycle and read at the end of a cycle. Therefore, an ID stage will return the results of a WB state occurring during the same cycle. See Section and Figure for details.

c Suppose you executed the code on a version of the pipeline from Section that handles data hazards by simply stalling the pipeline ie inserting NOP instructions where necessary Show the pipeline timing diagram below when the code is executed.

table#IFIDEXMEM,WB#

d Suppose you executed the code below on a pipeline from Section that uses data forwarding for handling data hazards. Show the pipeline timing diagram below:

table#IFIDEXMEM,WB#

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock