Question: Consider the pipelined processor below, Assume the following -Branch instructions are 15% of the executed instructions in assembly language programs. The remainder are instructions that

Consider the pipelined processor below, Assume the following

-Branch instructions are 15% of the executed instructions in assembly language programs. The remainder are instructions that perform calculations (data instructions).

-Data hazards affect both branch and data instruction performance. Consider data instructions and branch instructions that do not have control hazard delays (correctly predicted branch instructions). Assume these instructions have an average CPI of 1.2 (due to data hazards).

-Control hazards also affect performance, but I'm not going to directly give you this number. Instead, consider all instructions (including incorrectly predicted branches). Assume overall average CPI for all instructions is 1.3.

-For this problem, don't worry about jump instructions. For control hazards, you will need to consider delays imposed by incorrectly predicted branches.

-branch outcome is determined in the REG stage, and assume branch prediction (and instruction cancelling, when appropriate) is used to resolve control hazards.

What is the accuracy of the branch predictor?

Hint: Write the algebra formula for a weighted average using the information above. The number of cycles for branch instructions with failed predictions is: 1.2 + some stall penalt(ies). You should have one unknown.

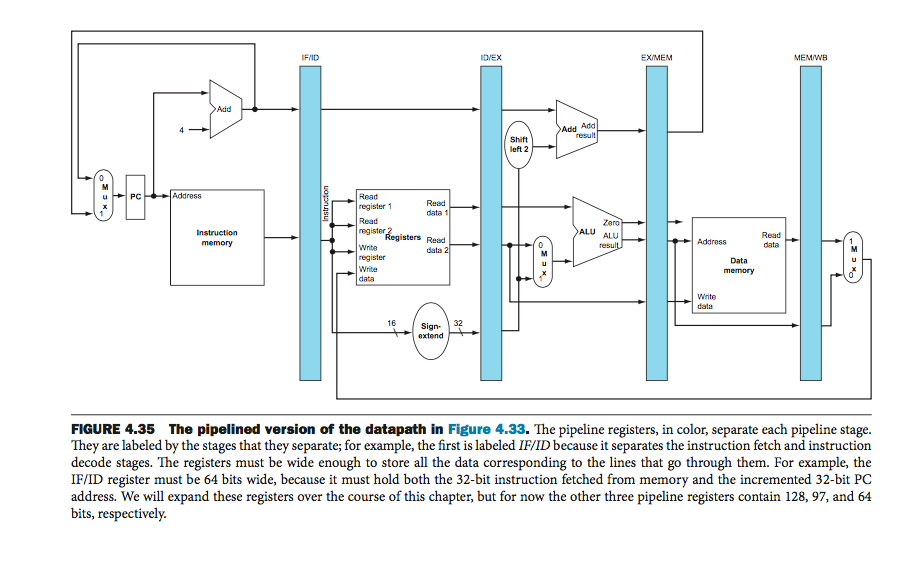

FNID EXMEM MEMIWE Add Add Add eft 2 MI register 1 data 1 Read register Registers Reed ALU data data Data data 16 Sign- 32 FIGURE 4.35 The pipelined version of the datapath in Figure 4.33. The pipeline registers, in color, separate each pipeline stage They are labeled by the stages that they separate; for example, the first is labeled IF/ID because it separates the instruction fetch and instruction decode stages. The registers must be wide enough to store all the data corresponding to the lines that go through them. For example, the IF/ID register must be 64 bits wide, because it must hold both the 32-bit instruction fetched from address. We will expand these registers over the course of this chapter, but for now the other three pipeline registers contain 128, 97, and 64 bits, respectively. memory and the incremented 32-bit PC FNID EXMEM MEMIWE Add Add Add eft 2 MI register 1 data 1 Read register Registers Reed ALU data data Data data 16 Sign- 32 FIGURE 4.35 The pipelined version of the datapath in Figure 4.33. The pipeline registers, in color, separate each pipeline stage They are labeled by the stages that they separate; for example, the first is labeled IF/ID because it separates the instruction fetch and instruction decode stages. The registers must be wide enough to store all the data corresponding to the lines that go through them. For example, the IF/ID register must be 64 bits wide, because it must hold both the 32-bit instruction fetched from address. We will expand these registers over the course of this chapter, but for now the other three pipeline registers contain 128, 97, and 64 bits, respectively. memory and the incremented 32-bit PC

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts