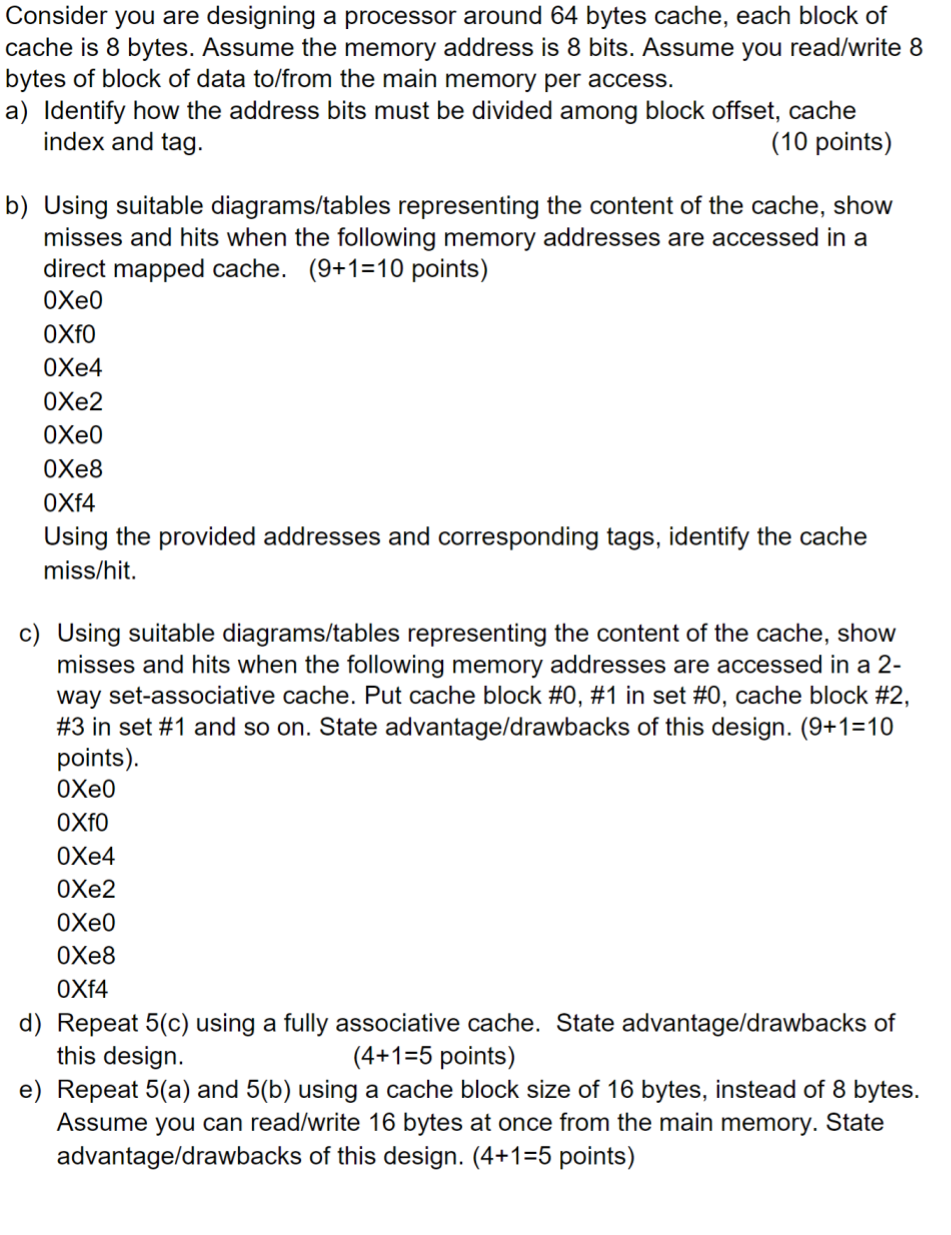

Question: Consider you are designing a processor around 6 4 bytes cache, each block of cache is 8 bytes. Assume the memory address is 8 bits.

Consider you are designing a processor around bytes cache, each block of

cache is bytes. Assume the memory address is bits. Assume you readwrite

bytes of block of data tofrom the main memory per access.

a Identify how the address bits must be divided among block offset, cache

index and tag.

points

b Using suitable diagramstables representing the content of the cache, show

misses and hits when the following memory addresses are accessed in a

direct mapped cache. points

OXe

OXfO

Xe

Xe

Xe

Xf

Using the provided addresses and corresponding tags, identify the cache

misshit

c Using suitable diagramstables representing the content of the cache, show

misses and hits when the following memory addresses are accessed in a

way setassociative cache. Put cache block # # in set # cache block #

# in set # and so on State advantagedrawbacks of this design.

points

OXe

OXfO

Xe

Xe

Xe

Xf

d Repeat c using a fully associative cache. State advantagedrawbacks of

this design.

points

e Repeat a and b using a cache block size of bytes, instead of bytes.

Assume you can readwrite bytes at once from the main memory. State

advantagedrawbacks of this design. points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock