Question: control signal which controls the Register File, must be 1 for all instructions that write a value to a The destination register, .eg for instructions

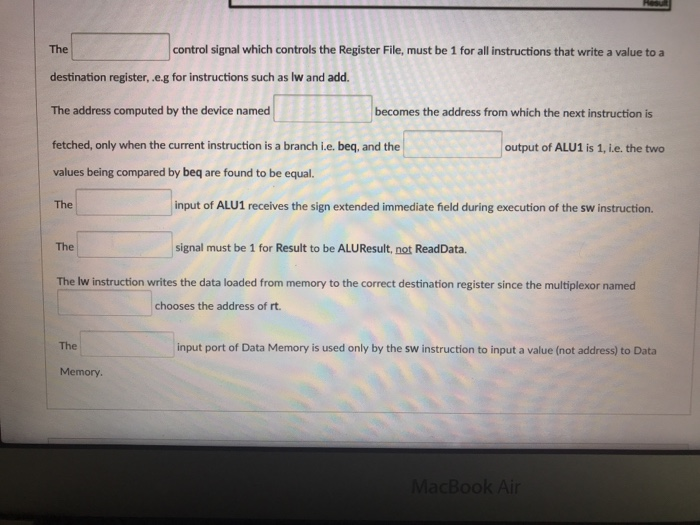

control signal which controls the Register File, must be 1 for all instructions that write a value to a The destination register, .eg for instructions such as lw and add. The address computed by the device named fetched, only when the current instruction is a branch i.e. beq, and the values being compared by beq are found to be equal. The becomes the address from which the next instruction is output of ALU1 is 1, i.e. the two input of ALU1 receives the sign extended immediate field during execution of the sw instruction. The signal must be 1 for Result to be ALUResult, not ReadData. The lw instruction writes the data loaded from memory to the correct destination register since the multiplexor named chooses the address of rt. The input port of Data Memory is used only by the sw instruction to input a value (not address) to Data Memory

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts