Question: CPls for each instruction: mul -> 4 clock cycles in EXE stage. add/sub -> 1 clock cycle in EXE stage sw/lw -> 2 clock cycles

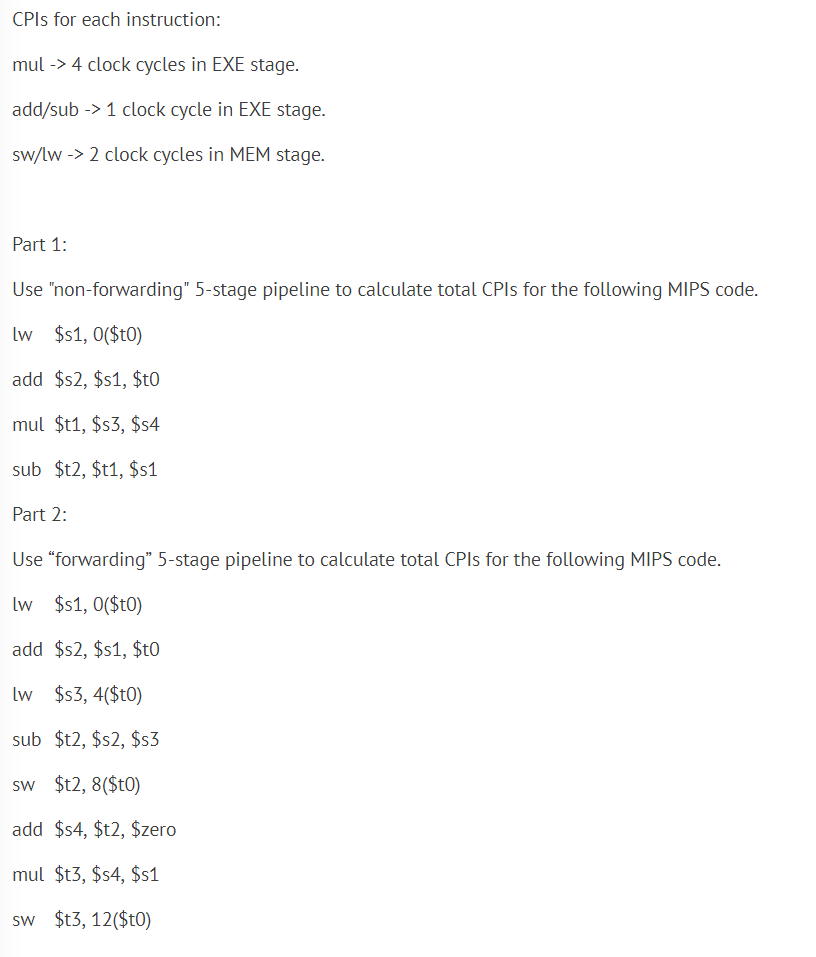

CPls for each instruction: mul -> 4 clock cycles in EXE stage. add/sub -> 1 clock cycle in EXE stage sw/lw -> 2 clock cycles in MEM stage Part 1 Use "non-forwarding" 5-stage pipeline to calculate total CPls for the following MIPS code lw $s1, 0($t0) add $s2, $s1, $t0 mul $t1, $s3, $s4 sub $t2, $t1, $s1 Part 2: Use forwarding" 5-stage pipeline to calculate total CPIs for the following MIPS code. lw $s1, 0($t0) add $s2, $s1, $t0 lw $S3, 4($t0) sub $t2, $s2, $s3 sw $t2, 8($t0) add $s4, $t2, $zero mul $t3, $s4, $s1 sw $t3, 12($t0)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts