Question: d) Assuming the register R1 contains value Ox20. Please write an ARM instruction that will update the NZCV bits of CPSR register as 0100: e)

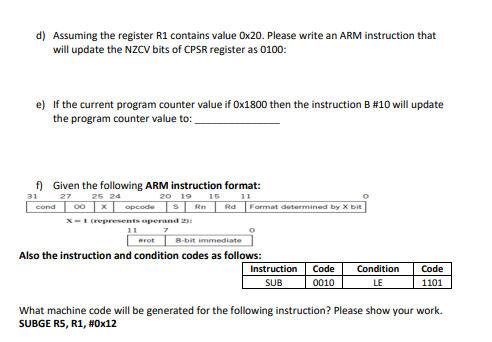

d) Assuming the register R1 contains value Ox20. Please write an ARM instruction that will update the NZCV bits of CPSR register as 0100: e) If the current program counter value if 0x1800 then the instruction B #10 will update the program counter value to: f) Given the following ARM instruction format: 31 27 25 24 20 19 15 cond 00pcode Rn Ra Format determined by x bit X-1 (represents operand 2): 11 wrot 8-bit immediate Also the instruction and condition codes as follows: Instruction Code Condition 0010 LE SUB Code 1101 What machine code will be generated for the following instruction? Please show your work. SUBGE R5, R1, #0x12 d) Assuming the register R1 contains value Ox20. Please write an ARM instruction that will update the NZCV bits of CPSR register as 0100: e) If the current program counter value if 0x1800 then the instruction B #10 will update the program counter value to: f) Given the following ARM instruction format: 31 27 25 24 20 19 15 cond 00pcode Rn Ra Format determined by x bit X-1 (represents operand 2): 11 wrot 8-bit immediate Also the instruction and condition codes as follows: Instruction Code Condition 0010 LE SUB Code 1101 What machine code will be generated for the following instruction? Please show your work. SUBGE R5, R1, #0x12

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts