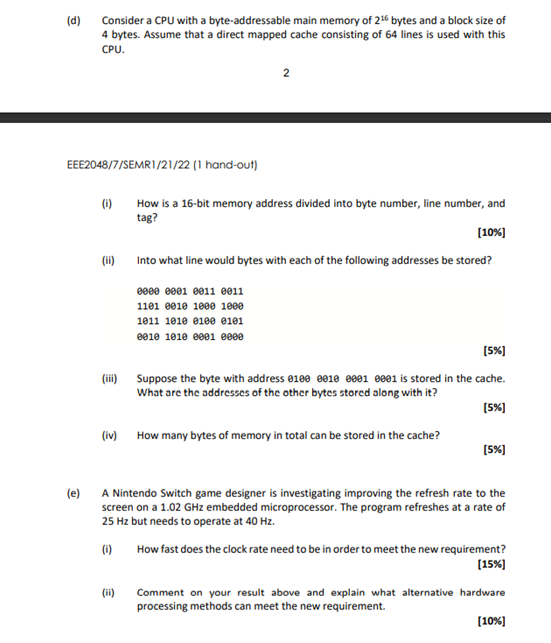

Question: (d) Consider a CPU with a byte-addressable main memory of 216 bytes and a block size of 4 bytes. Assume that a direct mapped cache

(d) Consider a CPU with a byte-addressable main memory of 216 bytes and a block size of 4 bytes. Assume that a direct mapped cache consisting of 64 lines is used with this CPU. 2 EEE2048/7/SEMR1/21/22 (1 hand-out) (1) How is a 16-bit memory address divided into byte number, line number, and tag? (10%) Into what line would bytes with each of the following addresses be stored? (ii) 8000 8001 0011 0011 1101 0010 1000 1000 1011 1010 0100 0101 2010 1010 0001 2000 [5%] (iii) ) Suppose the byte with address 918e ee1e eee1 eee1 is stored in the cache. What are the addresses of the other bytes stored along with it? [5%) (iv) How many bytes of memory in total can be stored in the cache? (5%) (e) e A Nintendo Switch game designer is investigating improving the refresh rate to the screen on a 1.02 GHz embedded microprocessor. The program refreshes at a rate of 25 Hz but needs to operate at 40 Hz. (1) How fast does the clock rate need to be in order to meet the new re requirement? (15%) (ii) Comment on your result above and explain what alternative hardware processing methods can meet the new requirement. (10%)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts