Question: d. Consider the following problem. A designer has a chip available and must decide what fraction of the chip will be devoted to cache memory

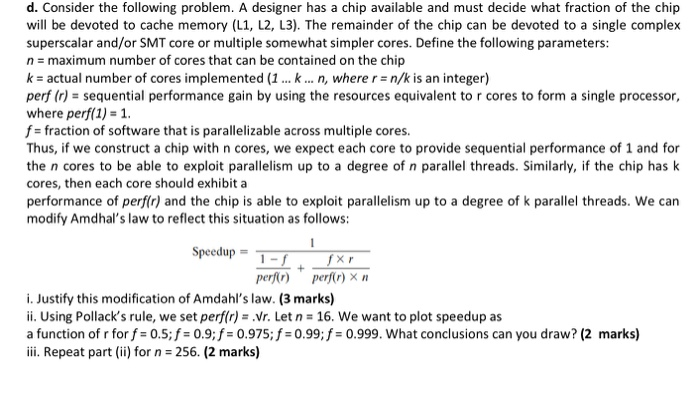

d. Consider the following problem. A designer has a chip available and must decide what fraction of the chip will be devoted to cache memory (L1, L2, L3). The remainder of the chip can be devoted to a single complex superscalar and/or SMT core or multiple somewhat simpler cores. Define the following parameters: n = maximum number of cores that can be contained on the chip k = actual number of cores implemented (1 ... k ... n, where r = n/k is an integer) perf (r) = sequential performance gain by using the resources equivalent to r cores to form a single processor, where perf(1) = 1. f = fraction of software that is parallelizable across multiple cores. Thus, if we construct a chip with n cores, we expect each core to provide sequential performance of 1 and for the n cores to be able to exploit parallelism up to a degree of n parallel threads. Similarly, if the chip has k cores, then each core should exhibit a performance of perf(r) and the chip is able to exploit parallelism up to a degree of k parallel threads. We can modify Amdhal's law to reflect this situation as follows: Speedup 1-S XP perfl perf(r) n i. Justify this modification of Amdahl's law. (3 marks) ii. Using Pollack's rule, we set perftr) = .vr. Let n = 16. We want to plot speedup as a function of r for f = 0.5; f = 0.9; f = 0.975; f = 0.99; f = 0.999. What conclusions can you draw? (2 marks) iii. Repeat part (ii) for n = 256. (2 marks) d. Consider the following problem. A designer has a chip available and must decide what fraction of the chip will be devoted to cache memory (L1, L2, L3). The remainder of the chip can be devoted to a single complex superscalar and/or SMT core or multiple somewhat simpler cores. Define the following parameters: n = maximum number of cores that can be contained on the chip k = actual number of cores implemented (1 ... k ... n, where r = n/k is an integer) perf (r) = sequential performance gain by using the resources equivalent to r cores to form a single processor, where perf(1) = 1. f = fraction of software that is parallelizable across multiple cores. Thus, if we construct a chip with n cores, we expect each core to provide sequential performance of 1 and for the n cores to be able to exploit parallelism up to a degree of n parallel threads. Similarly, if the chip has k cores, then each core should exhibit a performance of perf(r) and the chip is able to exploit parallelism up to a degree of k parallel threads. We can modify Amdhal's law to reflect this situation as follows: Speedup 1-S XP perfl perf(r) n i. Justify this modification of Amdahl's law. (3 marks) ii. Using Pollack's rule, we set perftr) = .vr. Let n = 16. We want to plot speedup as a function of r for f = 0.5; f = 0.9; f = 0.975; f = 0.99; f = 0.999. What conclusions can you draw? (2 marks) iii. Repeat part (ii) for n = 256. (2 marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts