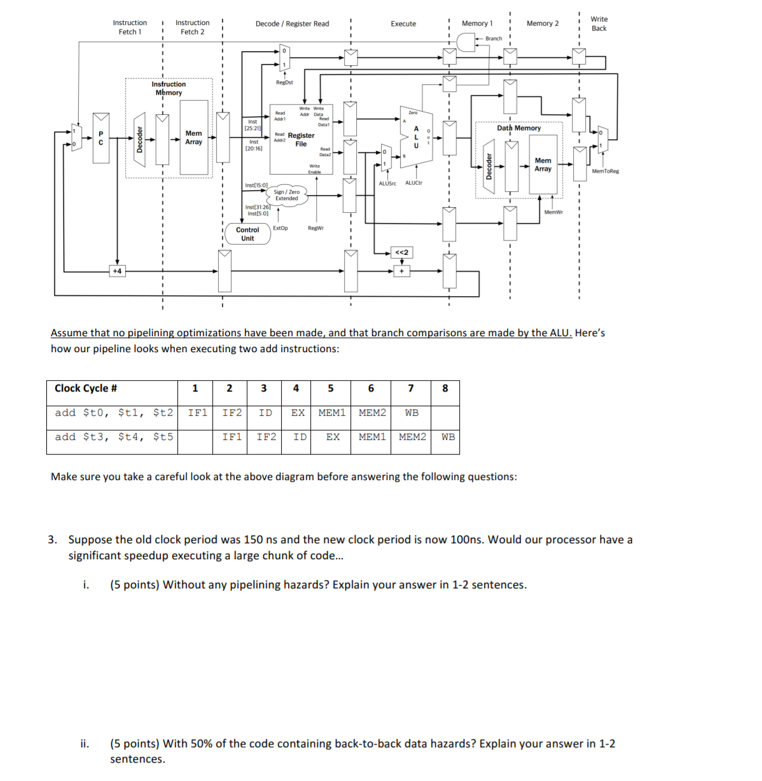

Question: Decode /Register Read Memory12 Execute Fetch 1I Fetch 2 I Back Dath Memory Register 20 6i nats on Control pRr Here's how our pipeline looks

Decode /Register Read Memory12 Execute Fetch 1I Fetch 2 I Back Dath Memory Register 20 6i nats on Control pRr Here's how our pipeline looks when executing two add instructions: Clock Cycle # add $t0, $t1, $t2 | IFI | 1F2| 1D | EX?MEM 11 MEM2 WB add $t3, $t4, $t5 Make sure you take a careful look at the above diagram before answering the following questions: Suppose the old clock period was 150 ns and the new clock period is now 100ns. Would our processor have a significant speedup executing a large chunk of code. i. 5 points) Without any pipelining hazards? Explain your answer in 1-2 sentences. ii. (5 points) with 50% of the code containing back-to-back data hazards? Explain your answer in 1-2 sentences

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts