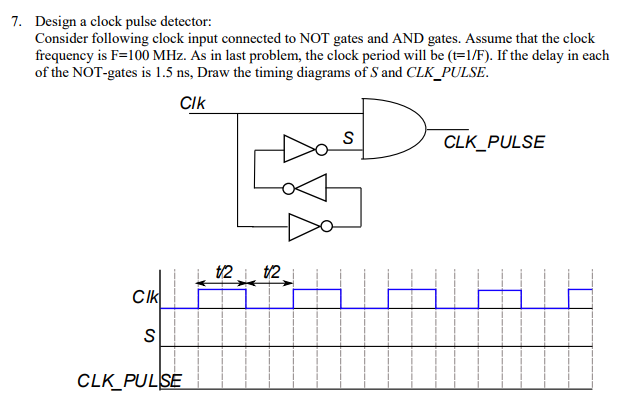

Question: Design a clock pulse detector: Consider following clock input connected to NOT gates and AND gates. Assume that the clock frequency is F= 100 MHz.

Design a clock pulse detector: Consider following clock input connected to NOT gates and AND gates. Assume that the clock frequency is F= 100 MHz. As in last problem , the clock period will be (t-VF). If the delay in each of the NOT-gates is 1.5 ns, Draw the timing diagrams of S and CLK_PULSE. 7. CIk CLK_PULSE Clk CLK_PULSELLL Design a clock pulse detector: Consider following clock input connected to NOT gates and AND gates. Assume that the clock frequency is F= 100 MHz. As in last problem , the clock period will be (t-VF). If the delay in each of the NOT-gates is 1.5 ns, Draw the timing diagrams of S and CLK_PULSE. 7. CIk CLK_PULSE Clk CLK_PULSELLL

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts