Question: Design a logic circuit using built-in primitives and behavioral Verilog, the circuit has 4 inputs and one output, the output Z will have the value

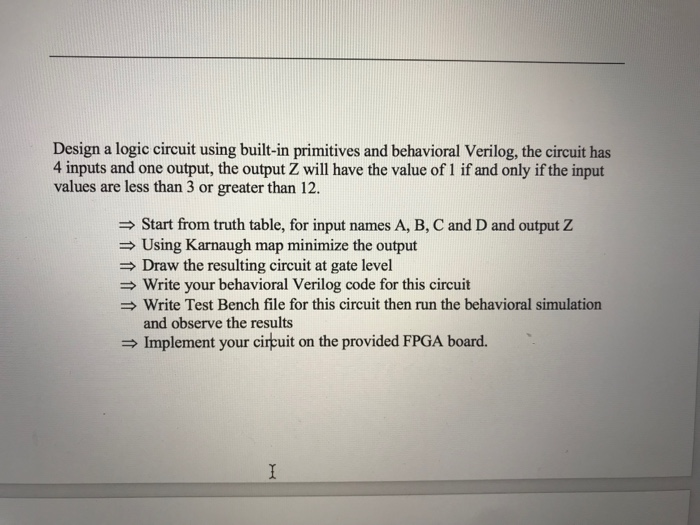

Design a logic circuit using built-in primitives and behavioral Verilog, the circuit has 4 inputs and one output, the output Z will have the value of 1 if and only if the input values are less than 3 or greater than 12. >Using Karnaugh map minimize the output >Write your behavioral Verilog code for this circuit >Implement your circuit on the provided FPGA board. Start from truth table, for input names A, B, C and D and output Z Draw the resulting circuit at gate level Write Test Bench file for this circuit then run the behavioral simulation and observe the results

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts