Question: Design a pattern recognizer with a single input x and a single output y that outputs a logic 1 when a pattern 1001 is observed,

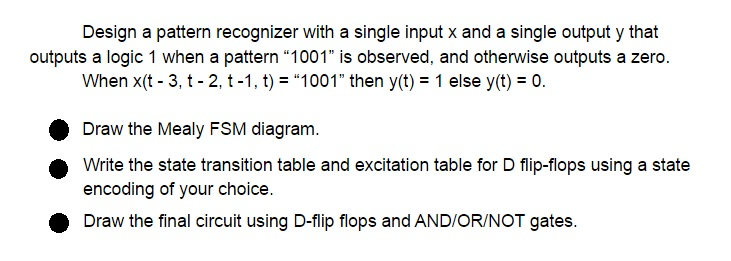

Design a pattern recognizer with a single input x and a single output y that outputs a logic 1 when a pattern "1001" is observed, and otherwise outputs a zero. When x(t - 3, t - 2, t-1, t) = "1001" then y(t) = 1 else y(t) = 0. Draw the Mealy FSM diagram. Write the state transition table and excitation table for D flip-flops using a state encoding of your choice. Draw the final circuit using D-flip flops and AND/OR/NOT gates

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts