Question: Design a sequential odd parity calculating and odd parity checking device as shown in the figure below. For this question you can use any flip

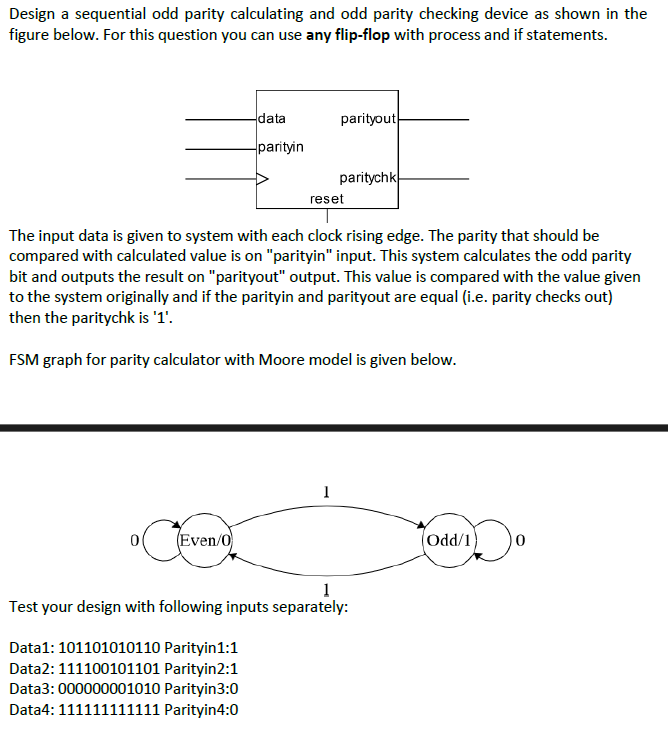

Design a sequential odd parity calculating and odd parity checking device as shown in the figure below. For this question you can use any flipflop with process and if statements.

The input data is given to system with each clock rising edge. The parity that should be compared with calculated value is on "parityin" input. This system calculates the odd parity bit and outputs the result on "parityout" output. This value is compared with the value given to the system originally and if the parityin and parityout are equal ie parity checks out then the paritychk is

FSM graph for parity calculator with Moore model is given below.

Test your desig

Data: Parityin:

Data: Parityin:

Data: Parityin:

Data: Parityin:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock