Question: Use Logisim Use logism Answer Question 3 3. Consider the modulo 2 sum of the bits of a 4-bit binary number. For example, 00000 ('even

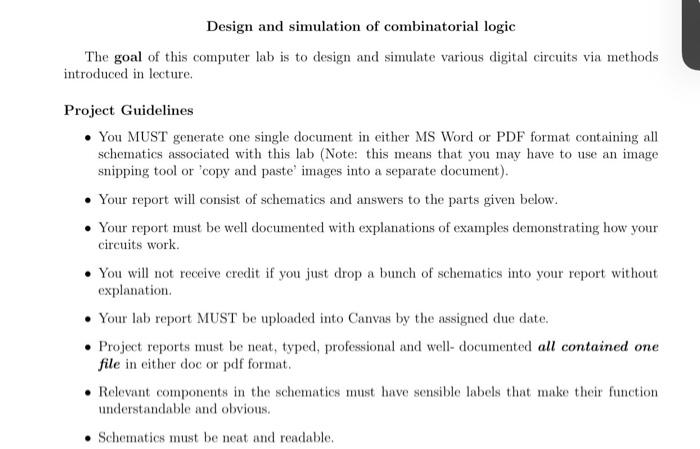

3. Consider the modulo 2 sum of the bits of a 4-bit binary number. For example, 00000 ('even parity'), 0001 + 1 (odd parity'), 0010 1 (odd parity'), 0011 + 0 ('even parity'), 0100 +1 ('odd parity'), 0101 + 0 ('even parity') and so on. i. Construct the truth table showing the modulo 2 sum of the bits for all possible 4-bit binary numbers ii. Use the minterm design procedure to simulate a circuit that will output the modulo 2 sum of the bits (ie the 'parity) for all possible input 4-bit binary numbers. iii. Verify the circuit operation by testing all possible input bit combinations listed in your truth table and report your results in your lab report. Design and simulation of combinatorial logle The goal of the design and it was dital circuits Project Guidelines . Yo SLUST gate decat sa Wed PDF chruticociated with the lab Note that you to whipping to our paste imagitante document) . Your post wit bewedl documented with patiempos dos by Yill be tetive coedit if you just kept into your eyes Your Lipo SIST bed to Cure by the end de date . retrobem el proberen down all contentcome file in the book pdf format Kelmet compete in the schematics at he malle labels showe use there waitsee establewo Design and Simulation Exercises I sine egned and mental de tradin yor totes FA L Asbewill peace Yo create the NV.CH I ny labut, you will ea talebing the released that verirYou will do the both The table will show the operanda, the expected and expected to the resultand the actual es wie Failure to produce this table for both addition and subtraction will render your circuit meer and no credit will be given. Coute but for your best full detector with hithe action to be a parte, and the late V.Ch This set will be able 2. A shit digital tes the pattern and to be the D+ high in an Luther . Fatract the people sites to col Biotin Dette bete blog Verify the latest testing alle bitte 1 Cadete 2 mol the software pe (ese purity). (odt.000 -- 1 (paits 001 - 0100-party.000 empurity and Contract the truth wing the mothers lie hinary 5. telo that is relab 3. Consider the modulo 2 sum of the bits of a 4-bit binary number. For example, 00000 ('even parity'), 0001 + 1 (odd parity'), 0010 1 ('odd parity'), 00110 ('even parity), 0100+1 'odd parity'), , 0101 + 0 ('even parity') and so on. i. Construct the truth table showing the modulo 2 sum of the bits for all possible 4-bit binary numbers. ii. Use the minterm design procedure to simulate a circuit that will output the modulo 2 sum of the bits (i.e. the 'parity') for all possible input 4-bit binary numbers. iii. Verify the circuit operation by testing all possible input bit combinations listed in your truth table and report your results in your lab report. 3. Consider the modulo 2 sum of the bits of a 4-bit binary number. For example, 0000 0 C'even parity'), 0001 + 1 (odd parity'), 0010 1 (odd parity'), 00110 ('even parity'), 0100 + 1 'odd parity'), .01010 ('even parity') and so on. i. Construct the truth table showing the modulo 2 sum of the bits for all possible 4-bit binary numbers. ii. Use the minterm design procedure to simulate a circuit that will output the modulo 2 sum of the bits (i.e. the 'parity) for all possible input 4-bit binary numbers. iii. Verify the circuit operation by testing all possible input bit combinations listed in your truth table and report your results in your lab report. Design and simulation of combinatorial logic The goal of this computer lab is to design and simulate various digital circuits via methods introduced in lecture. Project Guidelines You MUST generate one single document in either MS Word or PDF format containing all schematics associated with this lab (Note: this means that you may have to use an image snipping tool or 'copy and paste' images into a separate document). Your report will consist of schematics and answers to the parts given below. . Your report must be well documented with explanations of examples demonstrating how your circuits work . You will not receive credit if you just drop a bunch of schematics into your report without explanation Your lab report MUST be uploaded into Canvas by the assigned due date. Project reports must be neat, typed, professional and well-documented all contained one file in either doc or pdf format. Relevant components in the schematics must have sensible labels that make their function understandable and obvious. Schematics must be neat and readable

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts