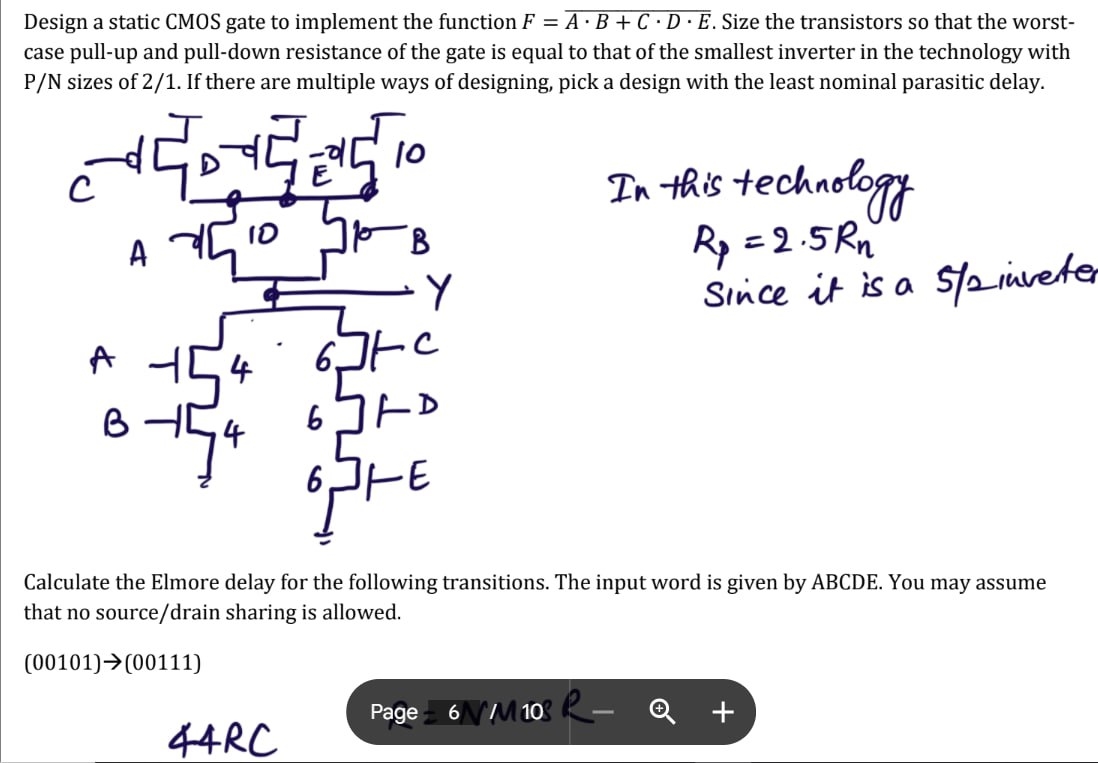

Question: Design a static CMOS gate to implement the function F ? b = a r ( A * B + C * D * E

Design a static CMOS gate to implement the function Size the transistors so that the worstcase pullup and pulldown resistance of the gate is equal to that of the smallest inverter in the technology with sizes of If there are multiple ways of designing, pick a design with the least nominal parasitic delay.

In this technology

since it is a inveter

Calculate the Elmore delay for the following transitions. The input word is given by ABCDE. You may assume that no sourcedrain sharing is allowed.

Page

rM

R

a

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock