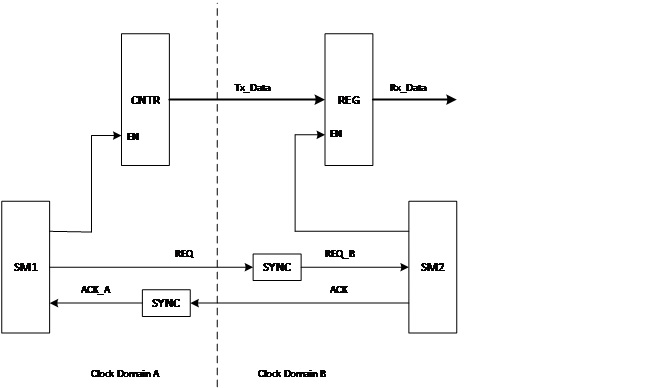

Question: Design a VHDL module that moves 16-bit data from a slow clock domain to a fast clock domain. Implement the following block diagram in VHDL.

Design a VHDL module that moves 16-bit data from a slow clock domain to a fast clock domain. Implement the following block diagram in VHDL.

Inputs: clk_a, clk_b, reset Outputs: Rx_Data

Part 1:

Building the Design Assume that reset is asynchronous for the counter, register and the state machines. The counter (CNTR) and the register (REG) should be 16-bits wide. Each should have an enable. Implement each function as its own VHDL process. Connect clk_a to the counter and connect the clk_b to the register. Design state machine 1 (SM1) as the transmit controller. Use clk_a for the state register. The initial state should increment the counter and immediately move to the next state. In the second state, assert the REQ signal. This machine should stay in the second state until the signal ACK_A is asserted. When ACK_A is asserted, go to a thirds state, de-assert REQ, wait for ACK_A to be de-asserted, and go back to the initial state. Design state machine 2 (SM2) as the receive controller. Use clk_b for the state register. In the initial state, the machine is waiting for REQ_B to be asserted. When REQ_B goes high, transition to the second state and enable the register. Immediately transition to a third state, de-assert the register enable, and wait for REQ_B to go low. When REQ_B is de-asserted, de-assert the ACK signal, and return to the initial state.

For the synchronizers (SYNC) write a VHDL module as a separate file. This module should just consist of two cascaded DFFs. In the top-level design, instantiate two SYNC modules. One should have clk_a and ACK connected as inputs and ACK_A as an output. The other should have clk_b and REQ connected as inputs and REQ_B as an output. Write a testbench for your design. Make a process for clk_a so that it is running at 11 MHz. Make a process for clk_b so that it is running at 100 MHz. Assert the reset for 100ns at the beginning of the simulation. Verify that the Rx_Data data changes the same order as the counter on the clk_a domain. Make sure that no values are skipped.

BM EN REOL SYNCle SM2 SYNC Cb DomanA Godk DomainB BM EN REOL SYNCle SM2 SYNC Cb DomanA Godk DomainB

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts