Question: Design an asynchronous process AsyncNotEnv that interacts with the process AsyncNot (Textbook Fig. 4.5, page 133). The process AsyncNotEnv has a Boolean input channel out

Design an asynchronous process AsyncNotEnv that interacts with the process AsyncNot (Textbook Fig. 4.5, page 133). The process AsyncNotEnv has a Boolean input channel out and a Boolean output channel in. It first outputs the value 0 and then is able to receive inputs. It waits until the received input equals and proceeds to output the value 1, and then waits until the received input equals 0. This cycle is then repeated. Answer the followings: a) Model the desired asynchronous process AsyncNotEnv as an extended-state machine. b) Consider the asynchronous composition AsyncNot | AsyncNotEnv and argue that (AsyncNot.mode hazard) is an invariant of the composite process.

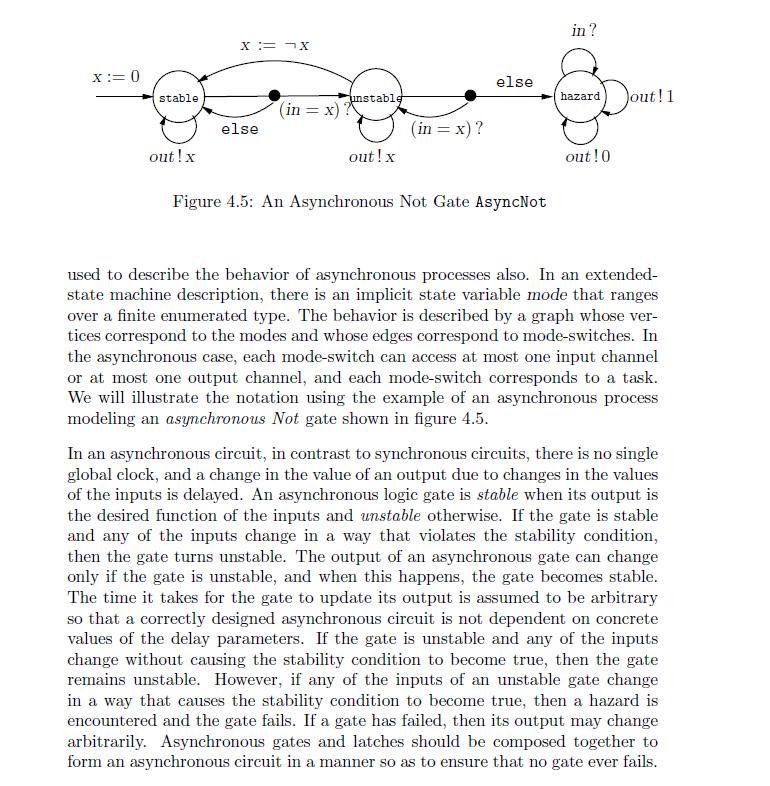

in? XX X=0 else stable hazard) out! 1 Jout!1 else unstable (in = x) (in = x)? out! x out! x out! Figure 4.5: An Asynchronous Not Gate AsyncNot used to describe the behavior of asynchronous processes also. In an extended- state machine description, there is an implicit state variable mode that ranges over a finite enumerated type. The behavior is described by a graph whose ver- tices correspond to the modes and whose edges correspond to mode-switches. In the asynchronous case, each mode-switch can access at most one input channel or at most one output channel, and each mode-switch corresponds to a task. We will illustrate the notation using the example of an asynchronous process modeling an asynchronous Not gate shown in figure 4.5. In an asynchronous circuit, in contrast to synchronous circuits, there is no single global clock, and a change in the value of an output due to changes in the values of the inputs is delayed. An asynchronous logic gate is stable when its output is the desired function of the inputs and unstable otherwise. If the gate is stable and any of the inputs change in a way that violates the stability condition, then the gate turns unstable. The output of an asynchronous gate can change only if the gate is unstable, and when this happens, the gate becomes stable. The time it takes for the gate to update its output is assumed to be arbitrary so that a correctly designed asynchronous circuit is not dependent on concrete values of the delay parameters. If the gate is unstable and any of the inputs change without causing the stability condition to become true, then the gate remains unstable. However, if any of the inputs of an unstable gate change in a way that causes the stability condition to become true, then a hazard is encountered and the gate fails. If a gate has failed, then its output may change arbitrarily. Asynchronous gates and latches should be composed together to form an asynchronous circuit in a manner so as to ensure that no gate ever fails. in? XX X=0 else stable hazard) out! 1 Jout!1 else unstable (in = x) (in = x)? out! x out! x out! Figure 4.5: An Asynchronous Not Gate AsyncNot used to describe the behavior of asynchronous processes also. In an extended- state machine description, there is an implicit state variable mode that ranges over a finite enumerated type. The behavior is described by a graph whose ver- tices correspond to the modes and whose edges correspond to mode-switches. In the asynchronous case, each mode-switch can access at most one input channel or at most one output channel, and each mode-switch corresponds to a task. We will illustrate the notation using the example of an asynchronous process modeling an asynchronous Not gate shown in figure 4.5. In an asynchronous circuit, in contrast to synchronous circuits, there is no single global clock, and a change in the value of an output due to changes in the values of the inputs is delayed. An asynchronous logic gate is stable when its output is the desired function of the inputs and unstable otherwise. If the gate is stable and any of the inputs change in a way that violates the stability condition, then the gate turns unstable. The output of an asynchronous gate can change only if the gate is unstable, and when this happens, the gate becomes stable. The time it takes for the gate to update its output is assumed to be arbitrary so that a correctly designed asynchronous circuit is not dependent on concrete values of the delay parameters. If the gate is unstable and any of the inputs change without causing the stability condition to become true, then the gate remains unstable. However, if any of the inputs of an unstable gate change in a way that causes the stability condition to become true, then a hazard is encountered and the gate fails. If a gate has failed, then its output may change arbitrarily. Asynchronous gates and latches should be composed together to form an asynchronous circuit in a manner so as to ensure that no gate ever fails

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts