Question: Design Problem Design a Mealy FSM that recognizes a binary input sequence satisfying the followings It includes odd number of 1 s It is an

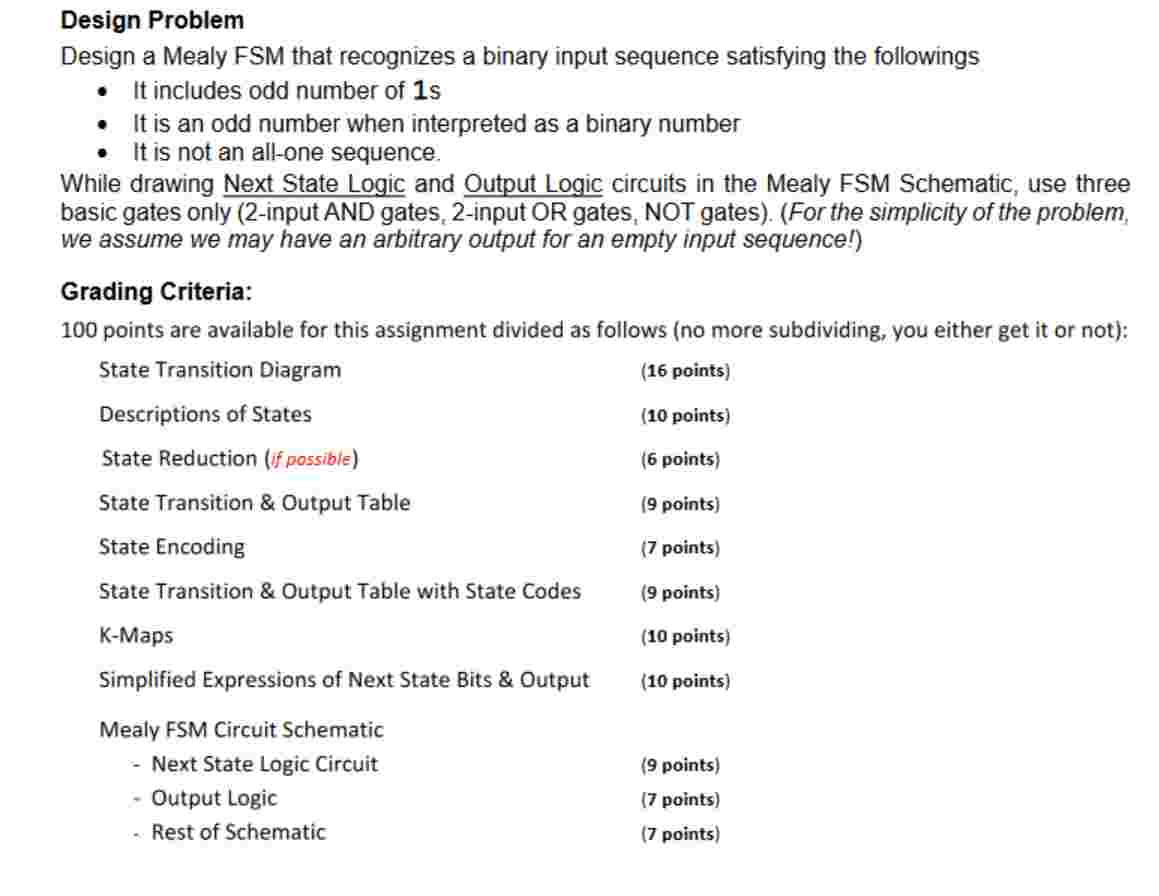

Design Problem

Design a Mealy FSM that recognizes a binary input sequence satisfying the followings

It includes odd number of s

It is an odd number when interpreted as a binary number

It is not an allone sequence.

While drawing Next State Logic and Output Logic circuits in the Mealy FSM Schematic, use three

basic gates only input AND gates, input OR gates, NOT gatesFor the simplicity of the problem,

we assume we may have an arbitrary output for an empty input sequence!

Grading Criteria:

points are available for this assignment divided as follows no more subdividing, you either get it or not:

State Transition Diagram points

Descriptions of States points

State Reduction if possible points

State Transition & Output Table points

State Encoding points

State Transition & Output Table with State Codes points

KMaps points

Simplified Expressions of Next State Bits & Output points

Mealy FSM Circuit Schematic

Next State Logic Circuit points

Output Logic points

Rest of Schematic points Design Problem

Design a Mealy FSM that recognizes a binary input sequence satisfying the followings

It includes odd number of s

It is an odd number when interpreted as a binary number

It is not an allone sequence.

While drawing Next State Logic and Output Logic circuits in the Mealy FSM Schematic, use three basic gates only input AND gates, input OR gates, NOT gatesFor the simplicity of the problem, we assume we may have an arbitrary output for an empty input sequence!

Grading Criteria:

points are available for this assignment divided as follows no more subdividing, you either get it or not:

State Transition Diagram

Descriptions of States

State Reduction if possible

State Transition & Output Table

State Encoding

State Transition & Output Table with State Codes

KMaps

Simplified Expressions of Next State Bits & Output

Mealy FSM Circuit Schematic

Next State Logic Circuit

Output Logic

Rest of Schematic

points

points

points

points

points

points

points

points

points

points

points

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock