Question: Design ROM subsystem, sized 16k words by 16 bits, using 4k-words-by-16-bit ROM chips. Design a ROM subsystem of size 16k words by 16 bits, using

Design ROM subsystem, sized 16k words by 16 bits, using 4k-words-by-16-bit ROM chips.

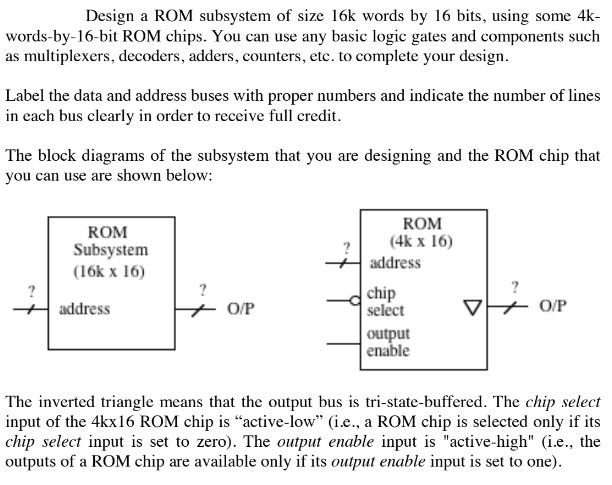

Design a ROM subsystem of size 16k words by 16 bits, using some 4k- words-by-16-bit ROM chips. You can use any basic logic gates and components such as multiplexers, decoders, adders, counters, etc. to complete your design Label the data and address buses with proper numbers and indicate the number of lines in each bus clearly in order to receive full credit The block diagrams of the subsystem that you are designing and the ROM chip that you can use are shown below ROM ROM Subsystem (16k x 16) ?(4k x 16) address chip select address O/P O/P output enable The inverted triangle means that the output bus is tri-state-buffered. The chip select input of the 4kx16 ROM chip is "active-low" (i.e., a ROM chip is selected only if its chip select input is set to zero). The output enable input is "active-high" (i.e., the outputs of a ROM chip are available only if its output enable input is set to one)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts