Question: don't use assign keywords Objective:To implement a Verilog gate level model for 3 2 - bit Signed multiplier. Outcome:Gate level implementation for the following components.

don't use assign keywords

Objective:To implement a Verilog gate level model for bit Signed multiplier.

Outcome:Gate level implementation for the following components.

MULTU MULT MUXx

Instruction: Complete gate level description of following components in mux.v file.

MUXx MUXx

Complete gate level description of following components in mult.v file

MULTU MULT

Compile entire Project and simulate following modules in ModelSim simulator.

MUXxTB MULTUTB MULTTB

Observe corresponding outcomes on waveform windows and fix any issue.

Each testbench will generate corresponding output file.

OUTPUTmuxxtbout OUTPUTmultutbout

OUTPUTmulttbout

Add more testing in these testbenches to make sure outcome is correct.

MUX.V file

bit mux

module MUXxlY I I S;

output list

output : Y;

input list

input : I;

input : I;

input S;

TBD

endmodule

bit mux

module MUXxYI I S;

output list

output Y;

input list

input I I S;

TBD

endmodule

MULT.V file

"include prjdefinition.v

module MULTHI LO A B ;

output list

output : HI;

output : LO;

input list

input : A;

input : B;

TBD

endmodule

module MULTUHI LO A B;

output list

output : HI;

output : LO;

input list

input : A;

input : B;

TBD

endmodule

this should be the output memory data file do not edit the following line required

for mem load use

instanceMULTTBresult

formathex addressradixh dataradixh version wordsperline noaddress

c

d

ffffffffffffff

ffffffffffffff

cf

cf

instanceMULTUTBresult

formathex addressradixh dataradixh version wordsperline noaddress

c

d

be

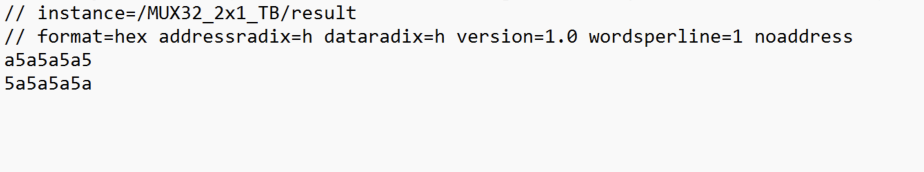

instanceMUXxTBresult

formathex addressradixh dataradixh version wordsperline noaddress

aaaa

aaaa

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock