Question: Edit the clock divider code included on the next page so that it meets the following three conditions Slowclock frequency = 1 Hz (or as

- Edit the clock divider code included on the next page so that it meets the following three conditions

- Slowclock frequency = 1 Hz (or as close as possible)

- MediumClock frequency = 2* SlowClock frequency

- FastClockFrequency = 2* MediumClock frequency

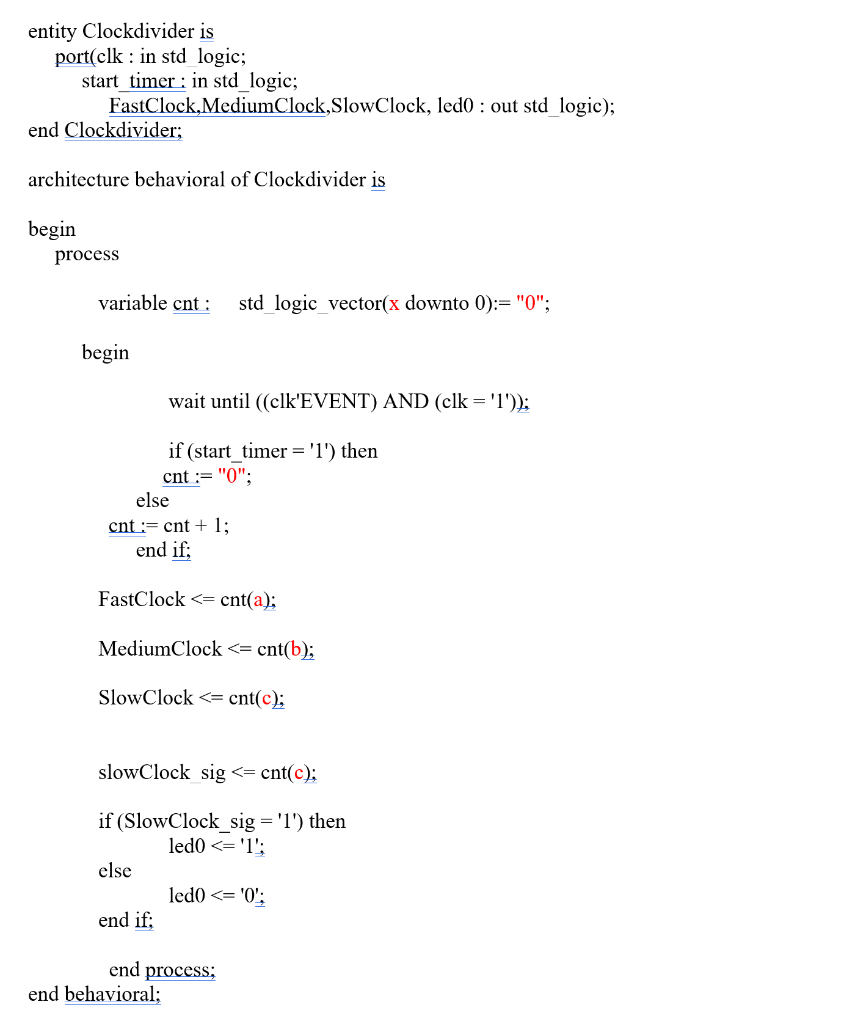

modify the portions of the code highlighted in red to divide your clock.

modify the portions of the code highlighted in red to divide your clock.

entity Clockdivider is port(clk : in std logic; start_timer : in std_logic; FastClock, MediumClock, Slow Clock, ledo : out std_logic); end Clockdivider; architecture behavioral of Clockdivider is begin process variable cnt : std logic vector(x downto 0):="0"; begin wait until ((clk'EVENT) AND (clk = '1')); if (start timer = '1') then cnt := "0"; else cnt :=cnt + 1; end if: FastClock

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts