Question: Exercise 2: You are given a non-pipelined processor design which has a cycle time of 10ns and average CPI of 1.4. Assume the base CPI

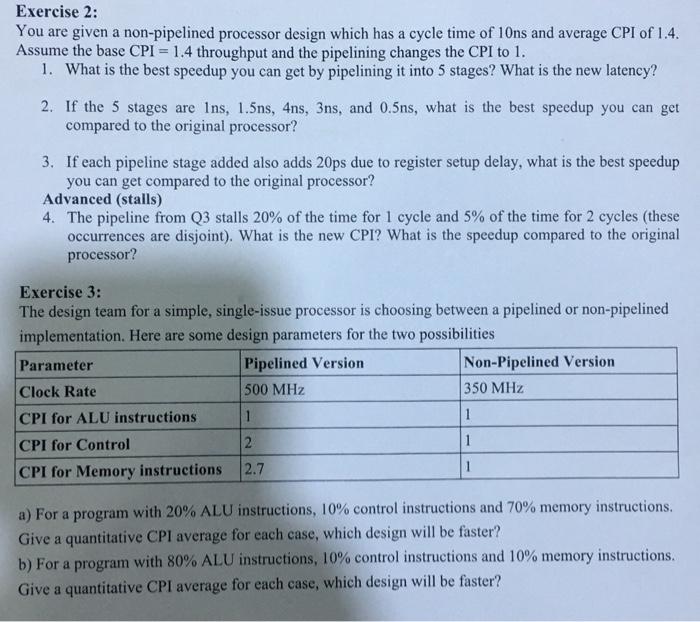

Exercise 2: You are given a non-pipelined processor design which has a cycle time of 10ns and average CPI of 1.4. Assume the base CPI = 1.4 throughput and the pipelining changes the CPI to 1. 1. What is the best speedup you can get by pipelining it into 5 stages? What is the new latency? 2. If the 5 stages are ins, 1.5ns, 4ns, 3ns, and 0.5ns, what is the best speedup you can get compared to the original processor? 3. If each pipeline stage added also adds 20ps due to register setup delay, what is the best speedup you can get compared to the original processor? Advanced (stalls) 4. The pipeline from Q3 stalls 20% of the time for 1 cycle and 5% of the time for 2 cycles (these occurrences are disjoint). What is the new CPI? What is the speedup compared to the original processor? Exercise 3: The design team for a simple, single-issue processor is choosing between a pipelined or non-pipelined implementation. Here are some design parameters for the two possibilities Parameter Pipelined Version Non-Pipelined Version Clock Rate 500 MHz 350 MHz CPI for ALU instructions 1 1 CPI for Control 2 CPI for Memory instructions 2.7 a) For a program with 20% ALU instructions, 10% control instructions and 70% memory instructions. Give a quantitative CPI average for each case, which design will be faster? b) For a program with 80% ALU instructions, 10% control instructions and 10% memory instructions. Give a quantitative CPI average for each case, which design will be faster

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts