Question: Exercise Write a right - shift SystemVerilog module that shifts the 8 - bit input data [ 7 : 0 right logically by the number

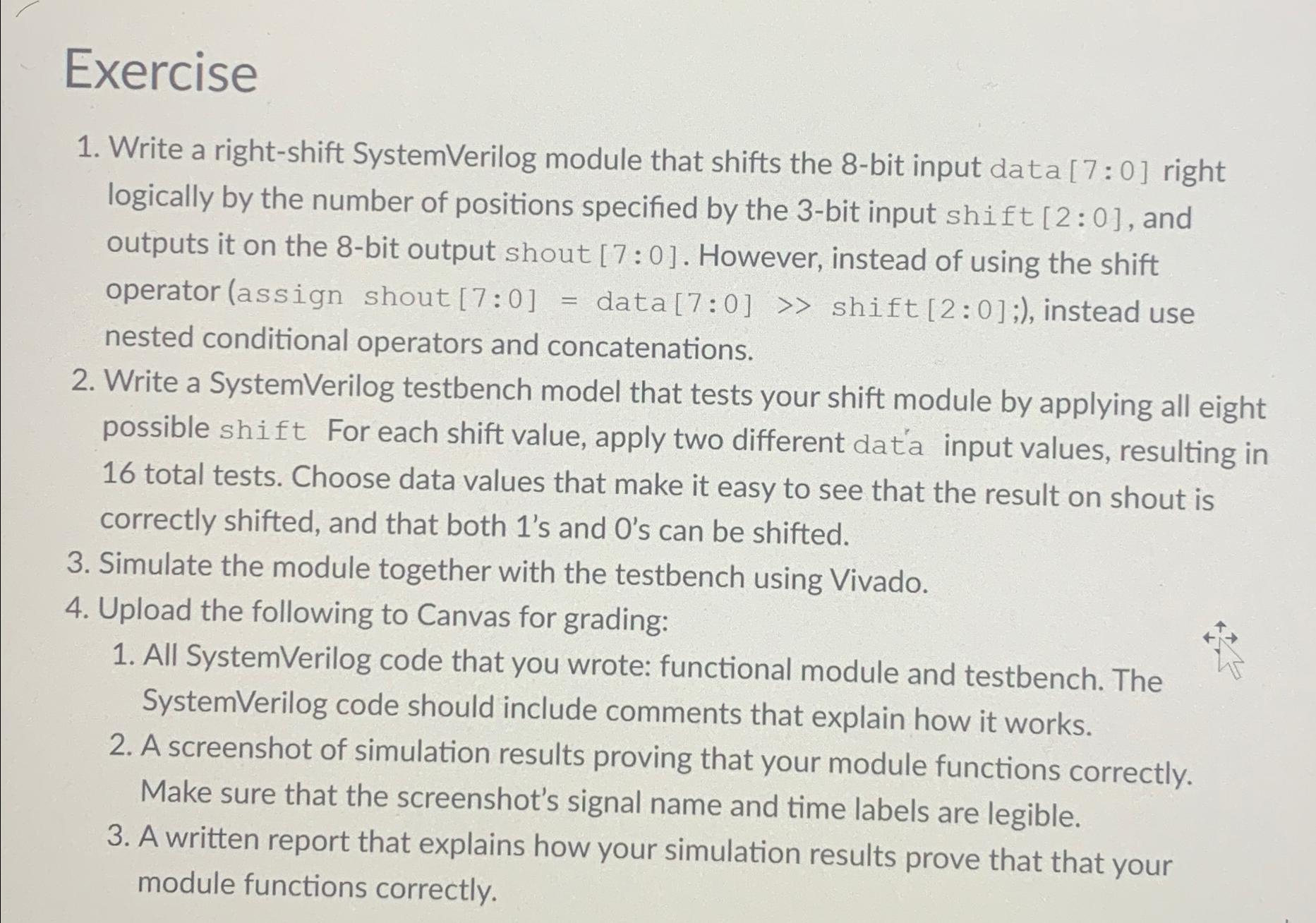

Exercise

Write a rightshift SystemVerilog module that shifts the bit input data : right logically by the number of positions specified by the bit input shift : and outputs it on the bit output shout : However, instead of using the shift operatorassign shout :data::; instead use nested conditional operators and concatenations.

Write a SystemVerilog testbench model that tests your shift module by applying all eight possible shift For each shift value, apply two different dat'a input values, resulting in total tests. Choose data values that make it easy to see that the result on shout is correctly shifted, and that both s and Os can be shifted.

Simulate the module together with the testbench using Vivado.

Upload the following to Canvas for grading:

All SystemVerilog code that you wrote: functional module and testbench. The SystemVerilog code should include comments that explain how it works.

A screenshot of simulation results proving that your module functions correctly. Make sure that the screenshot's signal name and time labels are legible.

A written report that explains how your simulation results prove that that your module functions correctly.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock