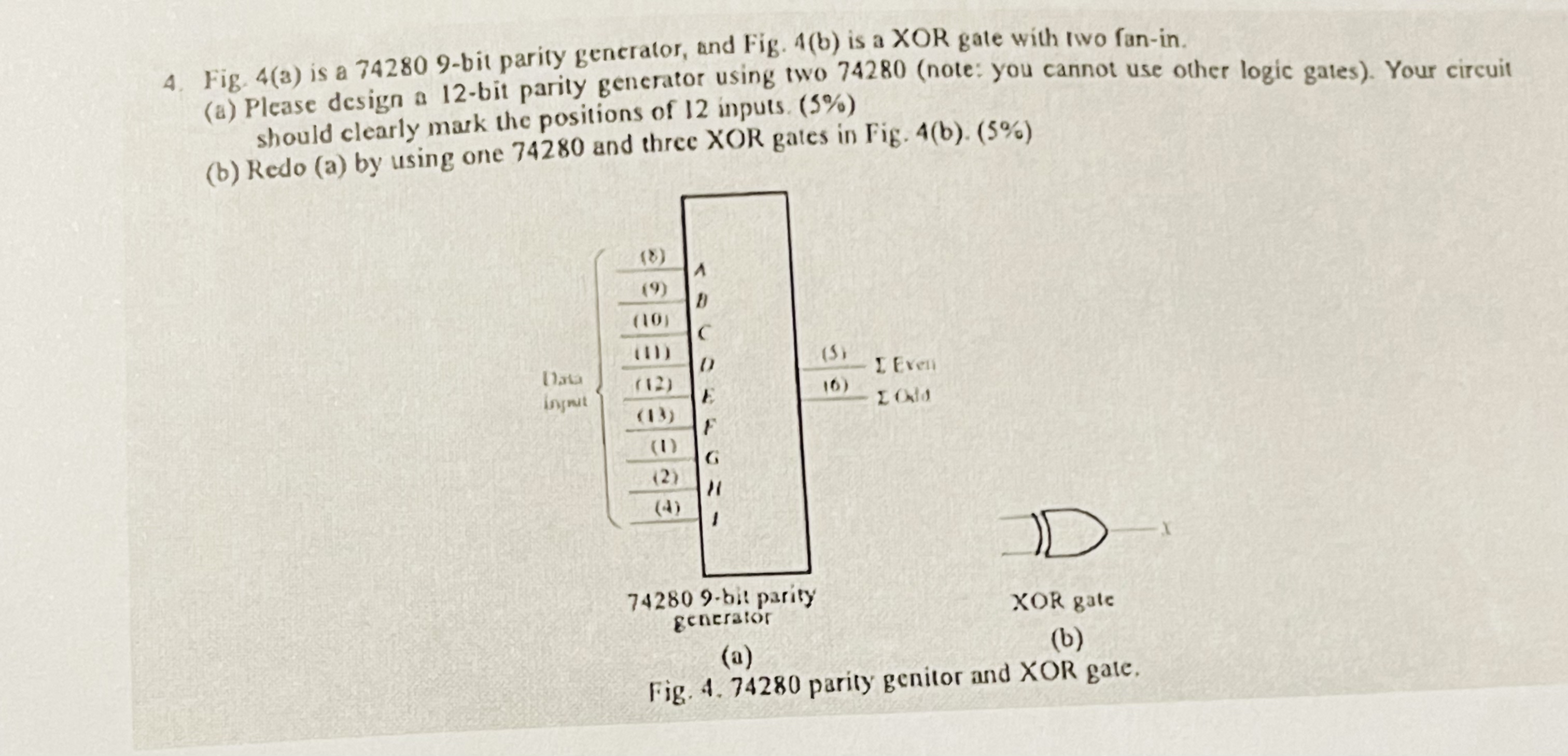

Question: Fig. 4 ( 3 ) is a 7 4 2 8 0 9 - bit parity gencrator, and Fig. 4 ( b ) is a

Fig. is a bit parity gencrator, and Fig. is a XOR gate with Iwo fanin

a Please design a bit parity generator using two note: you cannot use other logic gates Your circuit should clearly mark the positions of inputs.

b Redo a by using one and three XOR gates in Fig. b

a

XOR gate

b

Fig. parity genitor and XOR gate.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock