Question: Fill in missing code where its highlighted ( Q 1 ) Consider a parking lot with a single entry and exit gate. Two pairs of

Fill in missing code where its highlighted

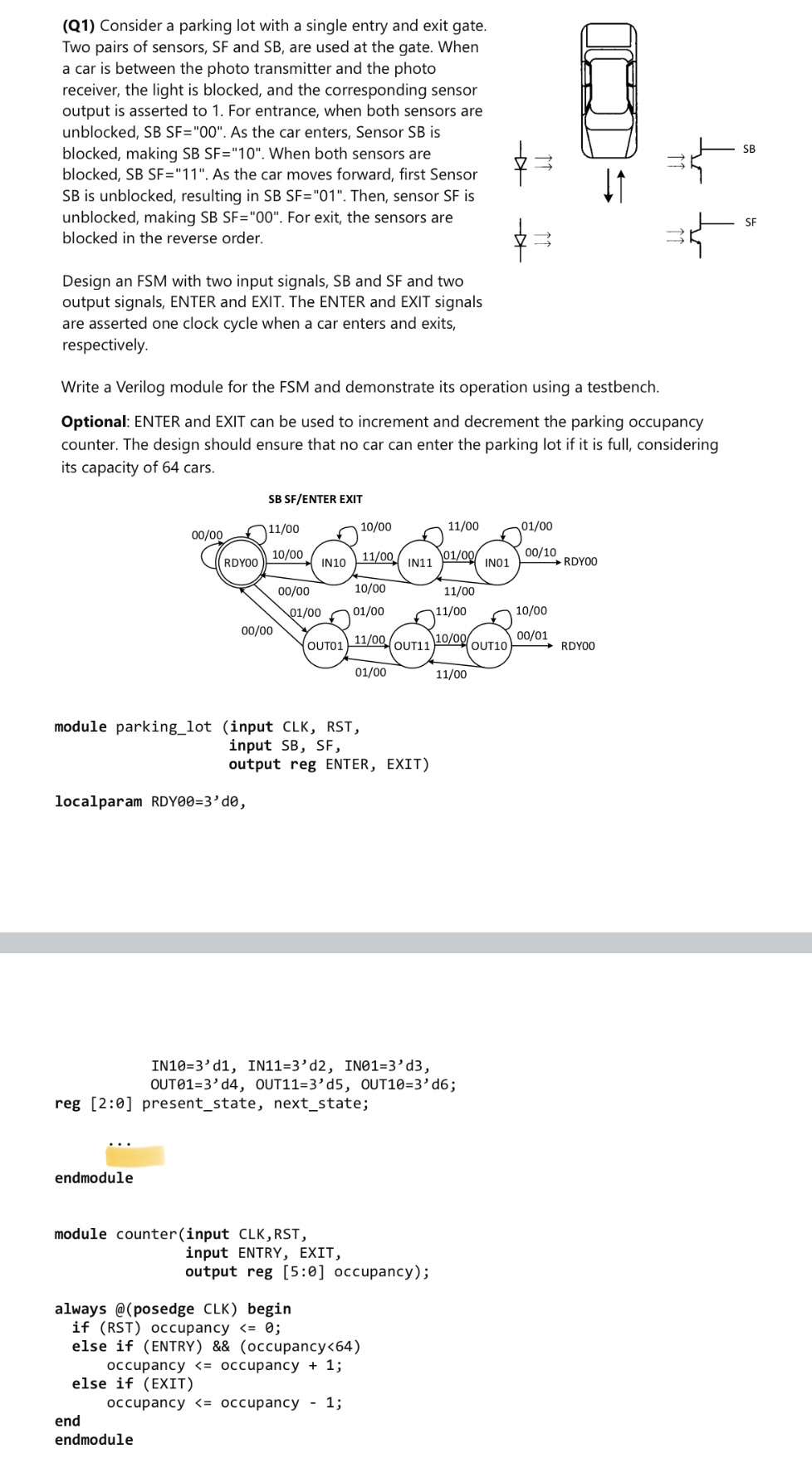

Q Consider a parking lot with a single entry and exit gate. Two pairs of sensors SF and SB are used at the gate. When a car is between the photo transmitter and the photo receiver, the light is blocked, and the corresponding sensor output is asserted to For entrance, when both sensors are unblocked, SB SF As the car enters, Sensor SB is blocked, making SB SF When both sensors are blocked, SB SF As the car moves forward, first Sensor is unblocked, resulting in SB SF Then, sensor SF is unblocked, making For exit, the sensors are blocked in the reverse order.

Design an FSM with two input signals, SB and SF and two output signals, ENTER and EXIT. The ENTER and EXIT signals are asserted one clock cycle when a car enters and exits, respectively.

Write a Verilog module for the FSM and demonstrate its operation using a testbench.

Optional: ENTER and EXIT can be used to increment and decrement the parking occupancy counter. The design should ensure that no car can enter the parking lot if it is full, considering its capacity of cars.localparam RDYOOd

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock