Question: Flash Memory - Your flash memory size is 4 Tbytes. - Each block contains 1 2 8 8 K - byte pages. - Address mapping

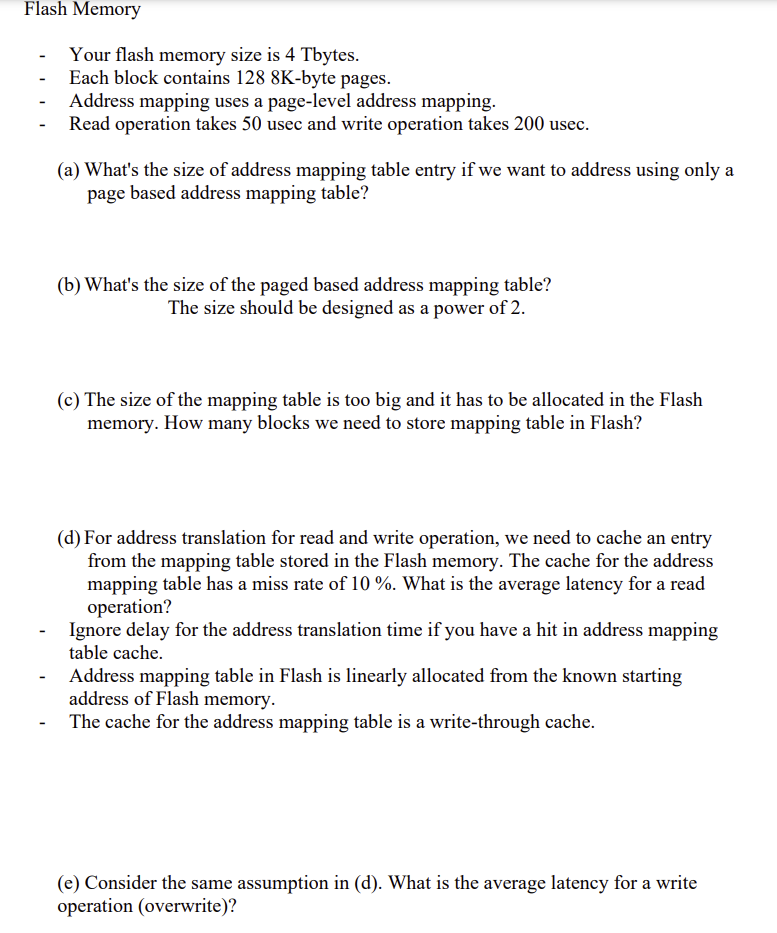

Flash Memory

Your flash memory size is Tbytes.

Each block contains Kbyte pages.

Address mapping uses a pagelevel address mapping.

Read operation takes usec and write operation takes usec.

a What's the size of address mapping table entry if we want to address using only a page based address mapping table?

b What's the size of the paged based address mapping table?

The size should be designed as a power of

c The size of the mapping table is too big and it has to be allocated in the Flash memory. How many blocks we need to store mapping table in Flash?

d For address translation for read and write operation, we need to cache an entry from the mapping table stored in the Flash memory. The cache for the address mapping table has a miss rate of What is the average latency for a read operation?

Ignore delay for the address translation time if you have a hit in address mapping table cache.

Address mapping table in Flash is linearly allocated from the known starting address of Flash memory.

The cache for the address mapping table is a writethrough cache.

e Consider the same assumption in d What is the average latency for a write operation overwrite

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock