Question: For a single-cycle design of a MIPS processor, how does instruction Ibu work based on its data flow along with the control signals? Using the

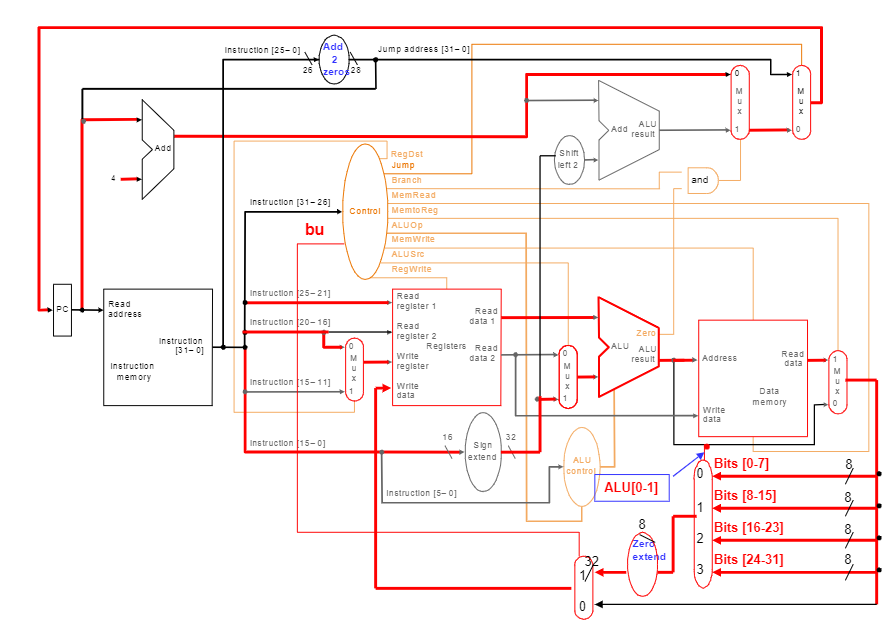

For a single-cycle design of a MIPS processor, how does instruction Ibu work based on its data flow along with the control signals? Using the HomeWork4-slides figure ("Circuit for Instruction Ibu") to explain all the related data flow and control signals within the single cycle. Please divide you single cycle into 5 stages: (1) instruction fetching, (2) instruction decoding, (3) ALU execution, (4) memory access, and (5) register writing. Note: Ibu: load byte unsigned from memory to register. Ibu $s1, 20($s2) # $s1 = Memory ([$s2 +20]) Jump address [31-01 Instruction [25-01 Add 2 26 \zero28 ALU Add result Add Shirt left 2 and Instruction (31-26] Regst Jump Branch MemRead Control Memo Reg ALUOP Mem Write ALUSTO Regwrite bu Instruction 25-21] PC Read address Instruction 20-16] Zero Instruction [31-01 Read register 1 Read data 1 Read register 2 Registers Read Write data 2 register Write data ALU ALU result Address Read data Instruction memory Instruction 15-111 Data memory 0 Write data 16 32 Instruction 15-0] Sign extend ALU control Bits (0-7] Instruction [5-01 ALU[O-1] Bits [8-15] 00000000 Bits (16-23] 8 Zera extend 2 Bits [24-31] 3 0 For a single-cycle design of a MIPS processor, how does instruction Ibu work based on its data flow along with the control signals? Using the HomeWork4-slides figure ("Circuit for Instruction Ibu") to explain all the related data flow and control signals within the single cycle. Please divide you single cycle into 5 stages: (1) instruction fetching, (2) instruction decoding, (3) ALU execution, (4) memory access, and (5) register writing. Note: Ibu: load byte unsigned from memory to register. Ibu $s1, 20($s2) # $s1 = Memory ([$s2 +20]) Jump address [31-01 Instruction [25-01 Add 2 26 \zero28 ALU Add result Add Shirt left 2 and Instruction (31-26] Regst Jump Branch MemRead Control Memo Reg ALUOP Mem Write ALUSTO Regwrite bu Instruction 25-21] PC Read address Instruction 20-16] Zero Instruction [31-01 Read register 1 Read data 1 Read register 2 Registers Read Write data 2 register Write data ALU ALU result Address Read data Instruction memory Instruction 15-111 Data memory 0 Write data 16 32 Instruction 15-0] Sign extend ALU control Bits (0-7] Instruction [5-01 ALU[O-1] Bits [8-15] 00000000 Bits (16-23] 8 Zera extend 2 Bits [24-31] 3 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts