For some reason a keep getting added like it suppose to be but I get

module alu

input : a Operand A

input : b Operand B

input : opcode, Operation opcode from FSM

input enable, Enable signal for ALU operation

output reg : result, ALU result

output reg divbyzero Flag to indicate division by zero

;

ALU Operations based on opcode

always @ begin

divbyzero ; Default to no division by zero

result b; Default to zero result

if enable begin

case opcode

b: result ab; Addition

b: result ab; Subtraction

b: result ab; Multiplication

b: begin Division

if b begin

result b;

divbyzero ;

end else begin

result ab;

end

end

b: result a&b; AND

b: result ab; OR

b: result a; Shift Left

b: result a; Shift Right

default: result b; Default case

endcase

end

end

endmodule

module alutb;

reg : a; Test Operand A

reg : b; Test Operand B

reg : opcode; Test Operation opcode

reg enable; Test Enable signal

wire : result; ALU result

wire divbyzero; Division by zero flag

Instantiate the ALU module

alu dut

aa

bb

opcodeopcode

enableenable

resultresult

divbyzerodivbyzero

;

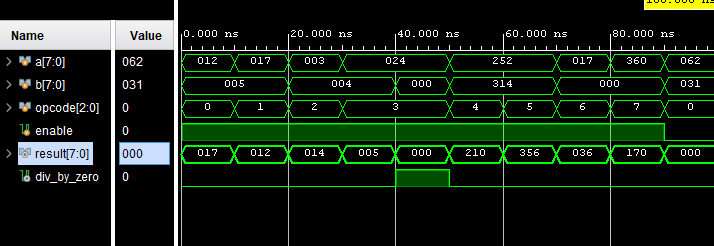

initial begin

Test cases

Test Addition

a d; b d; opcode b; enable ;

#;

Test Subtraction

a d; b d; opcode b; enable ;

#;

Test Multiplication

a d; b d; opcode b; enable ;

#;

Test Division No Error

a d; b d; opcode b; enable ;

#;

Test Division Division by Zero

a d; b d; opcode b; enable ;

#;

Test AND

a d; b d; opcode b; enable ; Binary: a b

#;

Test OR

a d; b d; opcode b; enable ; Binary: a b

#;

Test Shift Left

a d; b d; opcode b; enable ; Binary: a

#;

Test Shift Right

a d; b d; opcode b; enable ; Binary: a

#;

Test ALU Disabled

a d; b d; opcode b; enable ;

#;

$finish;

end

endmodule