Question: For the following instructions: ` ` ` A: load R 1 , e ( R 1 0 ) / / R 1 = MEM [

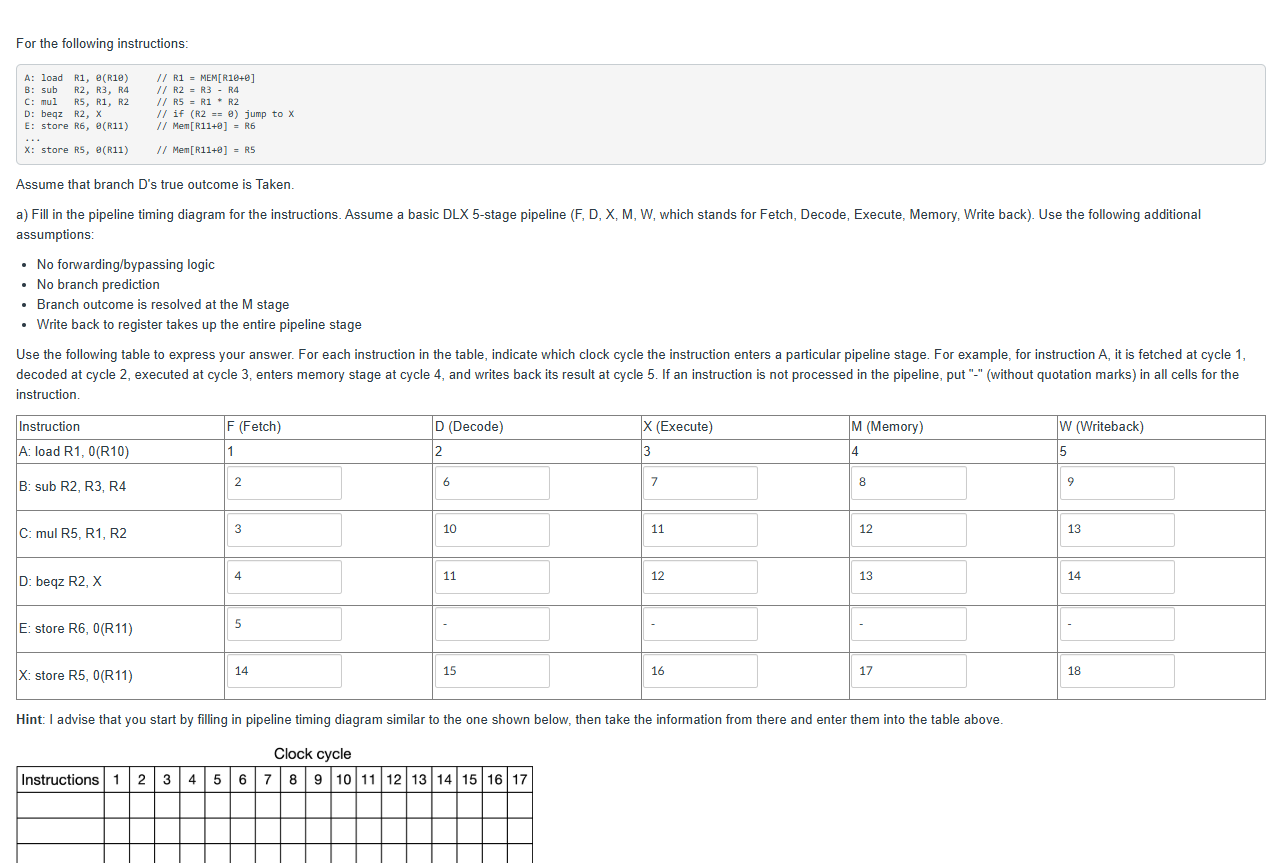

For the following instructions:

A: load R eR R MEMR

B: sub R R R R R R

C: mul R R R R R R

D: beqz R X if R jump to X

E: store RthetaR MemR R

X: store RR MemR R

Assume that branch Ds true outcome is Taken.

a Fill in the pipeline timing diagram for the instructions. Assume a basic DLX stage pipeline F D X M W which stands for Fetch, Decode, Execute, Memory, Write back Use the following additional assumptions:

No forwardingbypassing logic

No branch prediction

Branch outcome is resolved at the M stage

Write back to register takes up the entire pipeline stage

Use the following table to express your answer. For each instruction in the table, indicate which clock cycle the instruction enters a particular pipeline stage. For example, for instruction A it is fetched at cycle decoded at cycle executed at cycle enters memory stage at cycle and writes back its result at cycle If an instruction is not processed in the pipeline, put without quotation marks in all cells for the instruction.

Hint: I advise that you start by filling in pipeline timing diagram similar to the one shown below, then take the information from there and enter them into the table above.

Clock cycle

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock