Question: give me the first code only hdl by quartus Problem: Modeling a Multifunction ALU Design and implement a multifunction arithmetic and logic unit (ALU) based

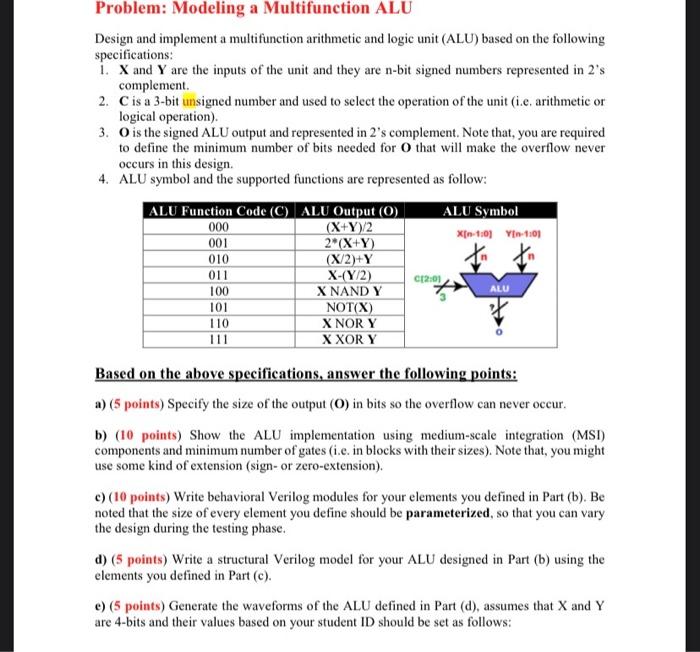

Problem: Modeling a Multifunction ALU Design and implement a multifunction arithmetic and logic unit (ALU) based on the following specifications: 1. X and Y are the inputs of the unit and they are n-bit signed numbers represented in 2's complement. 2. C is a 3-bit unsigned number and used to select the operation of the unit (i.e. arithmetic or logical operation). 3. O is the signed ALU output and represented in 2 's complement. Note that, you are required to define the minimum number of bits needed for O that will make the overflow never occurs in this design. 4. ALU symbol and the supported functions are represented as follow: Based on the above specifications, answer the following points: a) (5 points) Specify the size of the output (O) in bits so the overflow can never occur. b) (10 points) Show the ALU implementation using medium-scale integration (MSI) components and minimum number of gates (i.e. in blocks with their sizes). Note that, you might use some kind of extension (sign- or zero-extension). c) (10 points) Write behavioral Verilog modules for your elements you defined in Part (b). Be noted that the size of every element you define should be parameterized, so that you can vary the design during the testing phase. d) (5 points) Write a structural Verilog model for your ALU designed in Part (b) using the elements you defined in Part (c). e) (5 points) Generate the waveforms of the ALU defined in Part (d), assumes that X and Y are 4-bits and their values based on your student ID should be set as follows

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts